Intel® PXA255 Processor Developer’s Manual 10-3

UARTs

10.3 Signal Descriptions

Table 10-1 lists and describes each external signal that is connected to a UART module. The pins

are connected through the System Integration Unit to GPIOs. Refer to Section 4.1, “General-

Purpose I/O” on page 4-1 for details on the GPIOs.

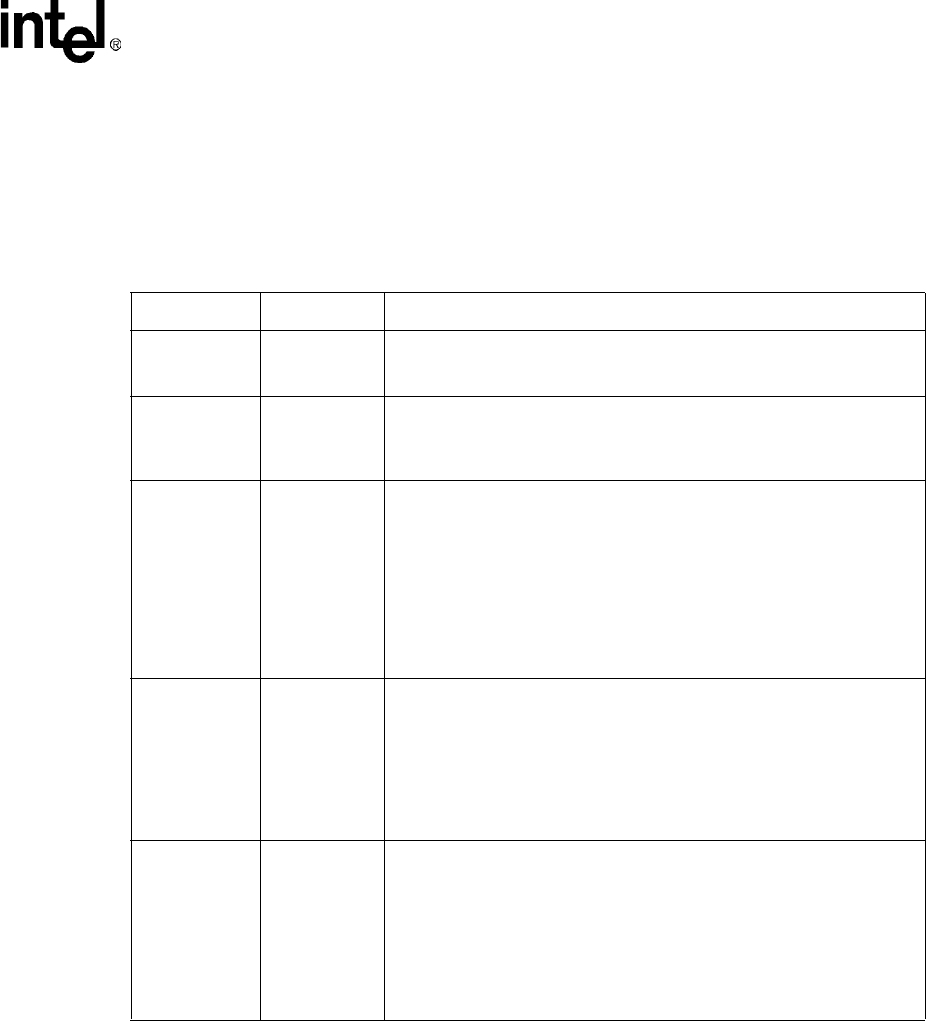

Table 10-1. UART Signal Descriptions (Sheet 1 of 2)

Name Type Description

RXD Input

SERIAL INPUT: Serial data input to the receive shift register. In infrared

mode, it is connected to the infrared receiver input. This signal is present on

all three UARTs.

TXD Output

SERIAL OUTPUT: Serial data output to the communications link-

peripheral, modem, or data set. The TXD signal is set to the logic 1 state

upon a Reset operation. It is connected to the output of the infrared

transmitter in infrared mode. This signal is present all three UARTs.

nCTS Input

CLEAR TO SEND: When low, indicates that the modem or data set is ready

to exchange data. The nCTS signal is a modem status input and its

condition can be tested by reading bit 4 (CTS) of the Modem Status

Register. Bit 4 is the complement of the nCTS signal. Bit 0 (DCTS) of the

Modem Status Register (MSR) indicates whether the nCTS input has

changed state since the last time the Modem Status Register was read.

nCTS has no effect on the transmitter. This signal is present on the

FFUART and BTUART.

When the CTS bit of the MSR changes state and the Modem Status

interrupt is enabled, an interrupt is generated.

nDSR Input

DATA SET READY: When low, indicates that the modem or data set is

ready to establish a communications link with a UART. The nDSR signal is

a Modem Status input and its condition can be tested by reading Bit 5

(DSR) of the MSR. Bit 5 is the complement of the nDSR signal. Bit 1

(DDSR) of the MSR indicates whether the nDSR input has changed state

since the MSR was last read. This signal is only present on the FFUART.

When the DSR bit of the MSR changes state, an interrupt is generated if the

Modem Status interrupt is enabled.

nDCD Input

DATA CARRIER DETECT: When low, indicates that the data carrier has

been detected by the modem or data set. The nDCD signal is a modem

status input and its condition can be tested by reading Bit 7 (DCD) of the

MSR. Bit 7 is the complement of the nDCD signal. Bit 3 (DDCD) of the MSR

indicates whether the nDCD input has changed state since the previous

reading of the Modem Status Register. nDCD has no effect on the receiver.

This signal is only present on the FFUART.

When the DCD bit changes state and the Modem Status interrupt is

enabled, an interrupt is generated.