Intel® PXA255 Processor Developer’s Manual 11-9

Fast Infrared Communication Port

3TXE

Transmit enable.

0 = FICP transmit logic disabled.

1 = FICP transmit logic enabled if ICCR0[ITR] is set.

All other control bits must be configured before TXE is set. An SIP is transmitted

immediately after the transmitter is enabled. If the transmit FIFO is empty, preambles are

sent until data is placed in the FIFO.

If TXE is cleared while it transmits data, transmission stops immediately, all data in the

transmit FIFO and serial output shifter is cleared, and the SIU takes control of the transmit

data pin.

While communication is normally half-duplex, it is possible to transmit and receive data at

the same time. Duplex communication is used for testing in Loopback Mode.

If TXE is used to clear the transmitter, check ICSR1[TBY] to ensure the transmitter is not

busy before the transmitter is re-enabled.

2TUS

Transmit FIFO underrun select.

A transmit FIFO underrun can either end the current frame normally, or transmit an abort.

0 = Transmit FIFO underrun causes CRC, stop flag, and SIP to be transmitted, and masks

transmit underrun interrupt generation.

1 = Transmit FIFO underrun causes abort to be transmitted, and generates an interrupt.

Clearing ICCR0[TUS] does not affect the current state of ICSR0[TUR] or prevent TUR from

being set or cleared by the transmit FIFO. After an abort, a SIP is transmitted followed by

16 preambles. Preambles continue until data is in the FIFO.

1LBM

Loopback mode.

Used for testing FICP.

0 = Normal FICP operation enabled.

1 = Output of transmit serial shifter is connected to input of receive serial shifter.

0ITR

IrDA transmission.

0 = ICP unit is not enabled.

1 = ICP unit is enabled.

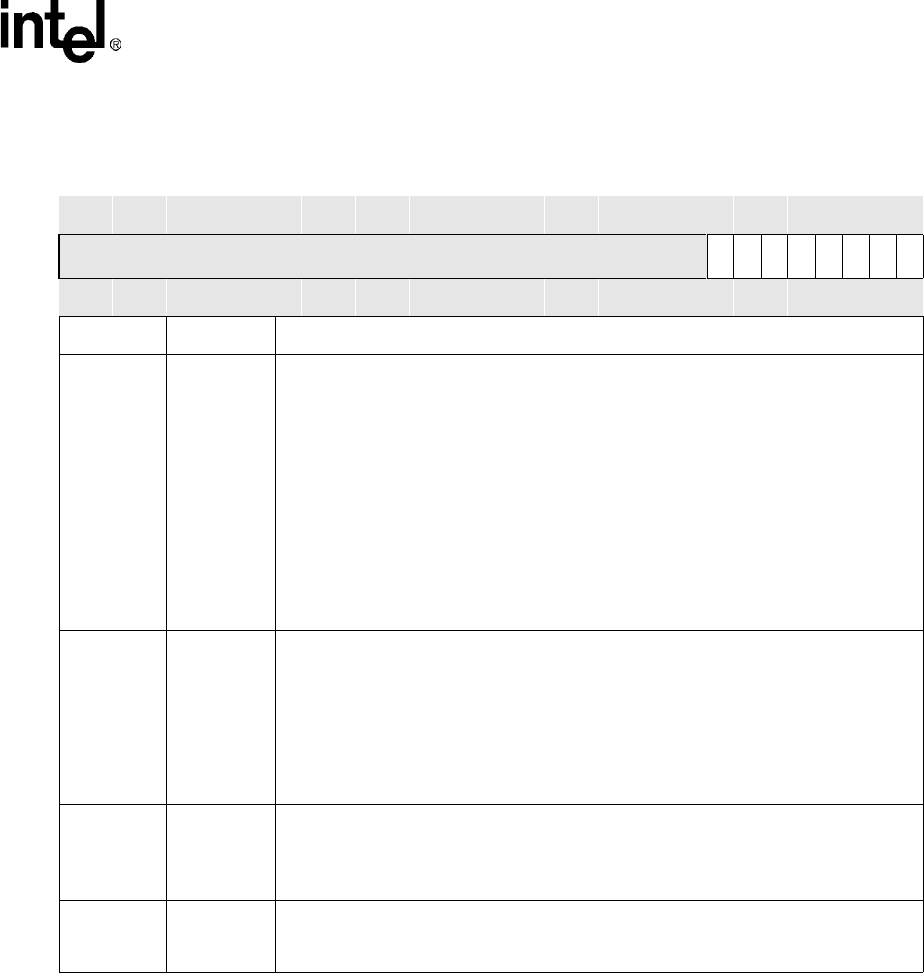

Table 11-2. ICCR0 Bit Definitions (Sheet 2 of 2)

0x4080_0000

Fast Infrared Communication Port

Control Register 0 (ICCR0)

Fast Infrared Communication Port

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

AME

TIE

RIE

RXE

TXE

TUS

LBM

ITR

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description