7-26 Intel® PXA255 Processor Developer’s Manual

LCD Controller

7.6.3 LCD Controller Control Register 2 (LCCR2)

LCCR2, shown in Table 7-5, contains four bit fields that are used as values for a collection of down

counters, each of which performs a different function to control the timing of several of the LCD’s

pins.

Beginning-of-Frame Line Clock Wait Count (BFW) — used in active mode (LCCR0[PAS] = 1)

to specify the number of line clocks to insert at the beginning of each frame. The BFW count starts

when the VSYNC signal for the previous frame is negated. The value in BFW is used to count the

number of line clock periods to insert before starting pixel output in the next frame. BFW generates

a wait period ranging from 0 to 255 extra L_LCLK cycles (BFW=0x00 disables the wait count).

L_LCLK does toggle during the generation of the BFW line clock wait periods.

In passive mode, BFW must be set to zero so that no beginning-of-frame wait states are generated.

Use VSW exclusively in passive mode to insert line clock wait states, which allow the LCD

controller’s DMAC to fill the palette and insert additional pixels before the start of the next frame.

End-of-Frame Line Clock Wait Count (EFW) — used in active mode (LCCR0[PAS] = 1) to

specify the number of line clocks to insert at the end of each frame. Once a complete frame of

pixels is transmitted to the LCD display, the value in EFW is used to count the number of line clock

periods to wait. After the count has elapsed, the VSYNC (L_FCLK) signal is pulsed. EFW

generates a wait period ranging from 0 to 255 line clock cycles (EFW = 0x00 disables the EOF

wait count). L_LCLK does not toggle during the generation of the EFW line clock periods.

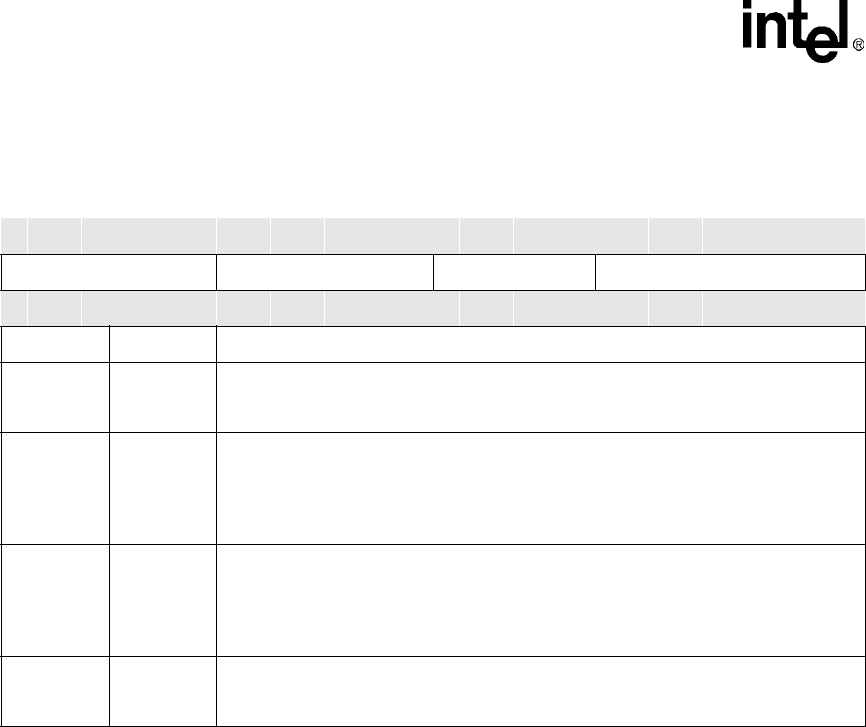

Table 7-4. LCCR1 Bit Definitions

Physical Address

0x4400_0004

LCD Controller Control Register 1 LCD Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

BLW ELW HSW PPL

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:24 BLW

Beginning-of-Line pixel clock Wait count:

Value (0–255) specifies the number of pixel clock periods to add to the beginning of a line

transmission before the first set of pixels is sent to the display. BOL wait = (BLW + 1).

23:16 ELW

End-of-line pixel clock wait count:

Value (0–255) specifies the number of pixel clock periods to add to the end of a line

transmission before line clock is asserted. EOL = (ELW+1).

In passive display mode, Pixel Clock is held in its inactive state during the end-of-line wait

period. In active display mode, it toggles.

15:10 HSW

Horizontal sync pulse width:

Value (0–63) specifies the number of pixel clock periods to pulse the line clock at the end of

each line. HSYNC pulse width = (HSW+1).

In passive display mode, Pixel Clock is held in its inactive state during the generation of the

line clock. In active display mode, it toggles.

9:0 PPL

Pixels per line:

Specifies the number of pixels contained within each line on the LCD display. Actual pixels

per line = (PPL+1).