4-44 Intel® PXA255 Processor Developer’s Manual

System Integration Unit

4.6 System Integration Unit Register Summary

4.6.1 GPIO Register Locations

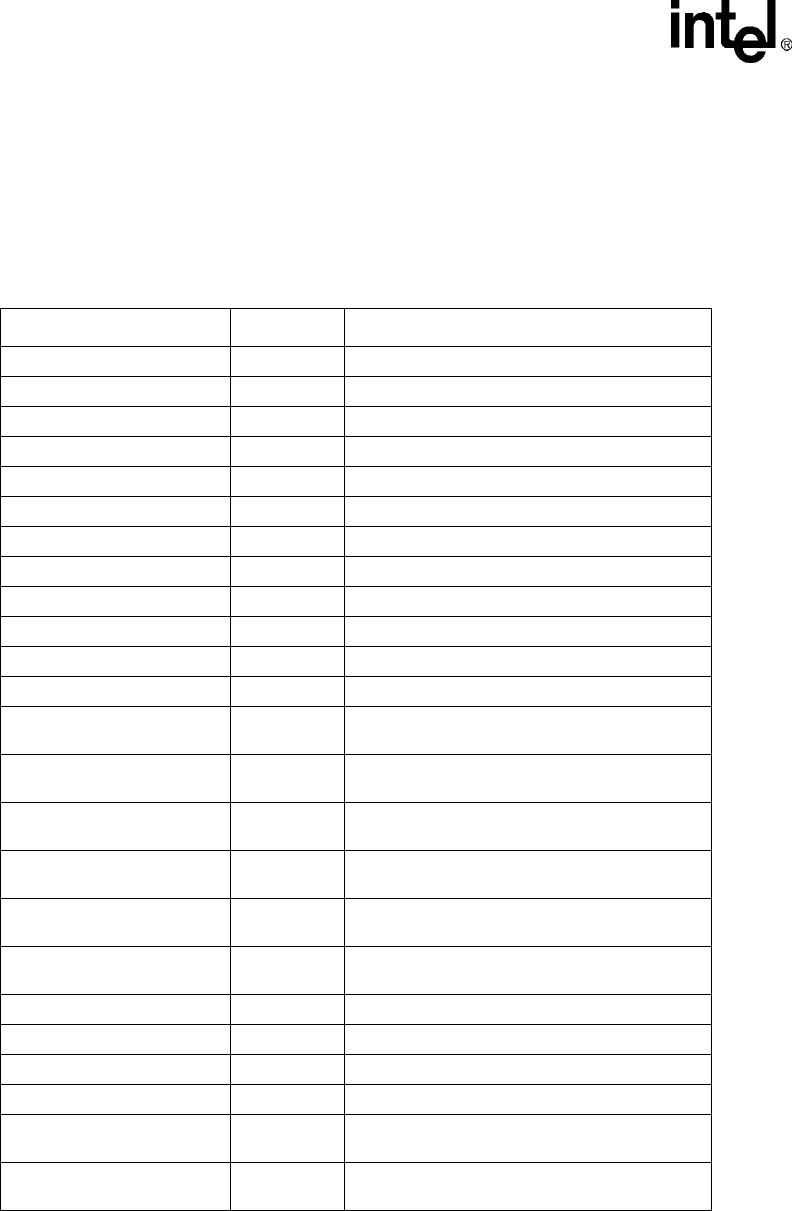

Table 4-49 shows the registers associated with the GPIO block and their physical addresses.

Table 4-49. GPIO Register Addresses (Sheet 1 of 2)

Address Name Description

0x40E0_0000 GPLR0 GPIO pin level register GPIO[31:0]

0x40E0_0004 GPLR1 GPIO pin level register GPIO[63:32]

0x40E0_0008 GPLR2 GPIO pin level register GPIO[80:64]

0x40E0_000C GPDR0 GPIO pin direction register GPIO[31:0]

0x40E0_0010 GPDR1 GPIO pin direction register GPIO[63:32]

0x40E0_0014 GPDR2 GPIO pin direction register GPIO[80:64]

0x40E0_0018 GPSR0 GPIO pin output set register GPIO[31:0]

0x40E0_001C GPSR1 GPIO pin output set register GPIO[63:32]

0x40E0_0020 GPSR2 GPIO pin output set register GPIO[80:64]

0x40E0_0024 GPCR0 GPIO pin output clear register GPIO[31:0]

0x40E0_0028 GPCR1 GPIO pin output clear register GPIO[63:32]

0x40E0_002C GPCR2 GPIO pin output clear register GPIO[80:64]

0x40E0_0030 GRER0

GPIO rising-edge detect enable register

GPIO[31:0]

0x40E0_0034 GRER1

GPIO rising-edge detect enable register

GPIO[63:32]

0x40E0_0038 GRER2

GPIO rising-edge detect enable register

GPIO[80:64]

0x40E0_003C GFER0

GPIO falling-edge detect enable register

GPIO[31:0]

0x40E0_0040 GFER1

GPIO falling-edge detect enable register

GPIO[63:32]

0x40E0_0044 GFER2

GPIO falling-edge detect enable register

GPIO[80:64]

0x40E0_0048 GEDR0 GPIO edge detect status register GPIO[31:0]

0x40E0_004C GEDR1 GPIO edge detect status register GPIO[63:32]

0x40E0_0050 GEDR2 GPIO edge detect status register GPIO[80:64]

0x40E0_0054 GAFR0_L GPIO alternate function select register GPIO[15:0]

0x40E0_0058 GAFR0_U

GPIO alternate function select register

GPIO[31:16]

0x40E0_005C GAFR1_L

GPIO alternate function select register

GPIO[47:32]