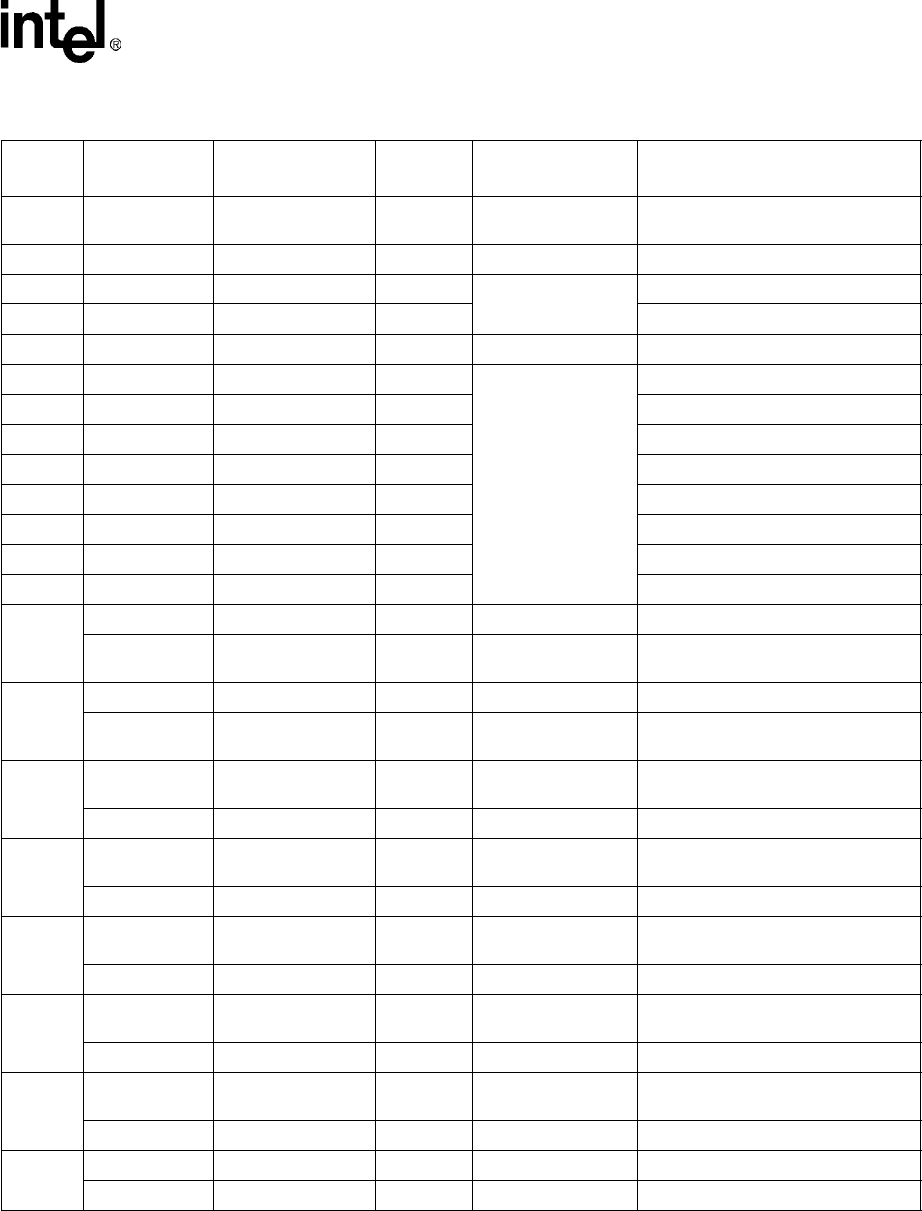

Intel® PXA255 Processor Developer’s Manual 4-5

System Integration Unit

GP54 MMCCLK ALT_FN_1_OUT 01

Multimedia Card

(MMC) Controller

MMC Clock

GP54 nPSKTSEL ALT_FN_2_OUT 10 Memory Controller Socket Select for Card Space

GP55 nPREG ALT_FN_2_OUT 10

Memory Controller

Card Address bit 26

GP56 nPWAIT ALT_FN_1_IN 01 Wait signal for Card Space

GP57 nIOIS16 ALT_FN_1_IN 01 Memory Controller Bus Width select for I/O Card Space

GP58

LDD[0] ALT_FN_2_OUT 10

LCD Controller

LCD data pin 0

GP59

LDD[1] ALT_FN_2_OUT 10 LCD data pin 1

GP60

LDD[2] ALT_FN_2_OUT 10 LCD data pin 2

GP61

LDD[3] ALT_FN_2_OUT 10 LCD data pin 3

GP62

LDD[4] ALT_FN_2_OUT 10 LCD data pin 4

GP63

LDD[5] ALT_FN_2_OUT 10 LCD data pin 5

GP64

LDD[6] ALT_FN_2_OUT 10 LCD data pin 6

GP65

LDD[7] ALT_FN_2_OUT 10 LCD data pin 7

GP66

LDD[8] ALT_FN_2_OUT 10 LCD Controller LCD data pin 8

MBREQ ALT_FN_1_IN 01 Memory Controller

memory controller alternate bus

master req

GP67

LDD[9] ALT_FN_2_OUT 10 LCD Controller LCD data pin 9

MMCCS0 ALT_FN_1_OUT 01

Multimedia Card

(MMC) Controller

MMC Chip Select 0

GP68

MMCCS1 ALT_FN_1_OUT 01

Multimedia Card

(MMC) Controller

MMC Chip Select 1

LDD[10] ALT_FN_2_OUT 10 LCD Controller LCD data pin 10

GP69

MMCCLK ALT_FN_1_OUT

01

Multimedia Card

(MMC) Controller

MMC_CLK

LDD[11] ALT_FN_2_OUT 10 LCD Controller LCD data pin 11

GP70

RTCCLK ALT_FN_1_OUT

01

System Integation

Unit

Real Time clock (1 Hz)

LDD[12] ALT_FN_2_OUT 10 LCD Controller LCD data pin 12

GP71

3.6 MHz ALT_FN_1_OUT

01

Clocks & Power

Manager Unit

3.6 MHz Oscillator clock

LDD[13] ALT_FN_2_OUT 10 LCD Controller LCD data pin 13

GP72

32 kHz ALT_FN_1_OUT

01

Clocks & Power

Manager Unit

32 kHz clock

LDD[14] ALT_FN_2_OUT 10 LCD Controller LCD data pin 14

GP73

LDD[15] ALT_FN_2_OUT 10 LCD Controller LCD data pin 15

MBGNT ALT_FN_1_OUT 01 Memory Controller Memory controller grant

Table 4-1. GPIO Alternate Functions (Sheet 3 of 4)

Pin

Alternate

Function Name

Alternate Function

Assignment

AF{n}

encoding

Source Unit Signal Description and comments