Intel® PXA255 Processor Developer’s Manual 5-5

DMA Controller

state is incremented, wrapping around from state machine state seven back to state machine state

zero. If there is no pending request, the state machine stays in the current state machine state until

there is a pending request. See Table 5-4 for priority scheme examples.

5.1.4 DMA Descriptors

The DMAC operates in two distinct modes: Descriptor Fetch Mode and No-Descriptor Fetch

Mode. The mode used is determined by the DCSRx[NODESCFETCH] bit.

The Descriptor Fetch and No-Descriptor modes can be used simultaneously on different channels.

This means that some DMA channels can be active in one mode while other channels are active in

the other mode.

A channel must be stopped before it can be switched from one mode to the other.

If an error occurs in a channel, it returns to its stopped state and remains there until software clears

the error condition and writes a 1 to the DCSR[RUN] register.

5.1.4.1 No-Descriptor Fetch Mode

In No-Descriptor Fetch Mode, the DDADRx is reserved. Software must not write to the DDADRx

and must load the DSADRx, DTADRx, and DCMDx registers. When the Run bit is set, the DMAC

immediately begins to transfer data. No-Descriptor fetches are performed at the beginning of the

transfer. The channel stops when it finishes the transfer.

Ensure that the software does not program the channel’s DDADx No-Descriptor Fetch Mode.

A typical No-Descriptor Fetch Mode (DCSR[NODESCFETCH] = 1) operation follows:

1. The channel is in an uninitialized state after reset.

2. The DCSR[RUN] bit is set to a 0 and the DCSR[NODESCFETCH] bit is set to a 1.

3. The software writes a source address to the DSADR register, a target address to the DTADR

register, and a command to the DCMD register. The DDADR register is reserved in this No-

Descriptor Fetch Mode and must not be written.

4. The software writes a 1 to the DCSR[RUN] bit and the No-Descriptor fetches are performed.

5. The channel waits for the request or starts the data transfer, as determined by the

DCMD[FLOW] source and target bits.

6. The channel transmits a number of bytes equal to the smaller of DCMD[SIZE] and

DCMD[LENGTH].

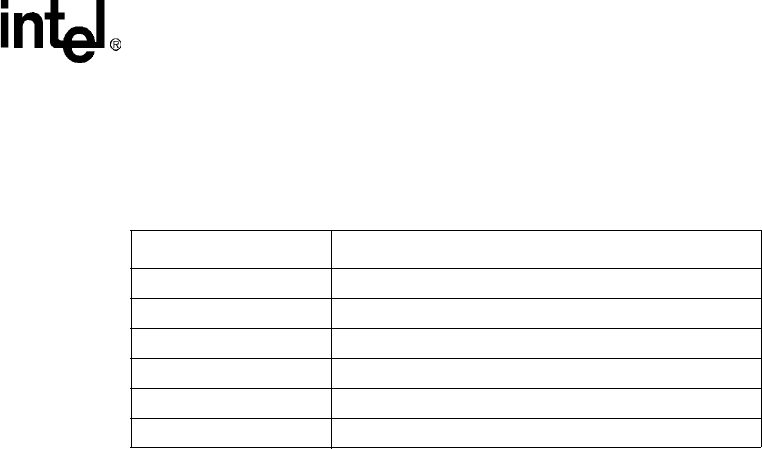

Table 5-4. Priority Schemes Examples

Channels Programmed DMA Channel Priority

ch0, ch1 0,1,0,1,0,1,0,1,etc.

ch0, ch15 0,0,0,15,0,0,0,15,etc.

ch0, ch4, ch8, ch12 0,4,0,8,0,4,0,12,etc.

ch0, ch1, ch8, ch12 0,1,0,8,0,1,0,12,etc.

ch0, ch4 0,4,0,0,0,4,0,4,etc.

ch8, ch12 8,12,8,8,8,12,8,12,etc.