15-32 Intel® PXA255 Processor Developer’s Manual

MultiMediaCard Controller

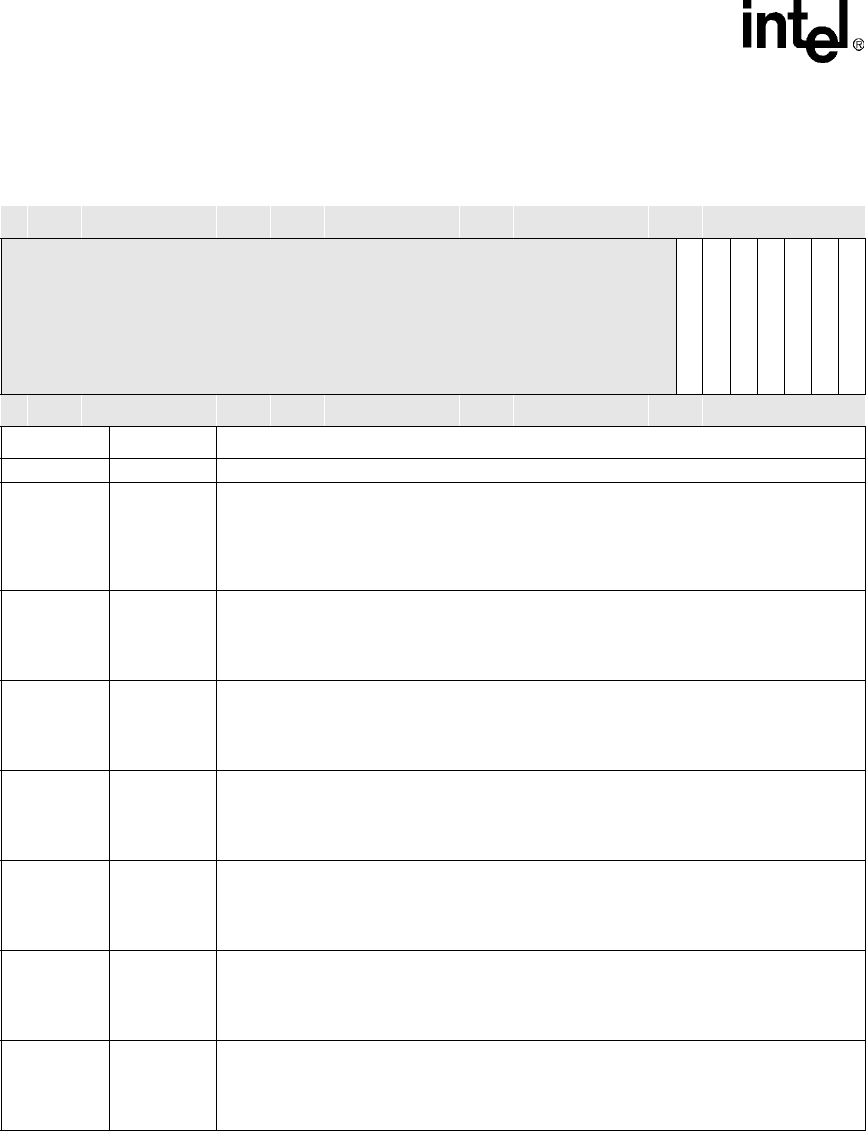

Table 15-16. MMC_I_REG Bit Definitions

Physical Address

0x4110_002c

MMC_I_REG Register MultiMediaCard Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

TXFIFO_WR_REQ

RXFIFO_RD_REQ

CLK_IS_OFF

STOP_CMD

END_CMD_RES

PRG_DONE

DATA_TRAN_DONE

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:5 — reserved

6

TXFIFO_WR_

REQ

Transmit FIFO Write Request

0 – No Request for data write to MMC_TXFIFO FIFO

1 – Request for data write to MMC_TXFIFO FIFO

Cleared after each write but immediately set again unless there are no entries left in the

FIFIO.

5

RXFIFO_RD_

REQ

Receive FIFO Read Request

0 – No Request for data read from MMC_RXFIFO FIFO

1 – Request for data read from MMC_RXFIFO FIFO

Cleared after each read but immediately set again unless the FIFO is empty.

4

CLK_IS_

OFF

Clock Is Off

0 – MMC clock has not been turned off

1 – MMC clock has been turned off, due to stop bit in STRP_CLK register

Cleared by the MMC_STAT[CLK_EN] bit when the clock is started.

3STOP_CMD

For stream mode writes.

0 – MMC is not ready for the stop transmission command

1 – MMC is ready for the stop transmission command

Cleared when CMD12 is loaded in the MMC_CMD register and the clock is started.

2

END_CMD_R

ES

End Command Response

0 – MMC has not received the response

1 – MMC has received the response or a response time-out has occurred

Cleared by the MMC_STAT[END_CMD_RES] bit.

1PRG_DONE

Programming Done

0 – Card has not finished programming and is busy

1 – Card has finished programming and is no longer busy

Cleared by the MMC_STAT[PRG_DONE] bit.

0

DATA_TRAN_

DONE

Data Transfer Done

0 – Data transfer is not complete

1 – Data transfer has completed or a read data time-out has occurred

Cleared by the MMC_STAT[DATA_TRAN_DONE] bit.