Intel® PXA255 Processor Developer’s Manual 13-23

AC’97 Controller Unit

13.8.3.3 PCM-Out Control Register (POCR)

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

6POINT

PCM Out Interrupt (POINT)

0 = None of the PCM out channel interrupts occurred.

1 = One of the PCM out channel interrupts occurred.

When the specific interrupt is cleared, this bit will be cleared (interruptible).

5PIINT

PCM In Interrupt (PIINT)

0 = None of the PCM in channel interrupts occurred.

1 = One of the PCM in channel interrupts occurred.

When the specific interrupt is cleared, this bit will be cleared (interruptible).

4:3 — reserved

2MOINT

Modem-Out Interrupt (MOINT)

0 = None of the Modem out channel interrupts occurred.

1 = One of the Modem out channel interrupts occurred.

When the specific interrupt is cleared, this bit will be cleared (interruptible).

1 MIINT

Modem-In Interrupt (MIINT)

0 = None of the modem-in channel interrupts occurred.

1 = One of the modem-in channel interrupts occurred.

When the specific interrupt is cleared, this bit will be cleared (interruptible).

0GSCI

CODEC GPI Status Change Interrupt (GSCI)

0 = Bit 0 of slot 12 is clear.

1 = Bit 0 of slot 12 is set. This indicates that one of the GPI’s changed state and that the

new values are available in slot 12.

The bit is cleared by software writing a “1” to this bit location (interruptible).

Table 13-8. GSR Bit Definitions (Sheet 2 of 2)

Physical Address

4050_001C

GSR Register AC’97 Controller Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

CDONE

SDONE

reserved

RDCS

BIT3SLT12

BIT2SLT12

BIT1SLT12

SECRES

PRIRES

SCR

PCR

MINT

POINT

PIINT

reserved

MOINT

MIINT

GSCI

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

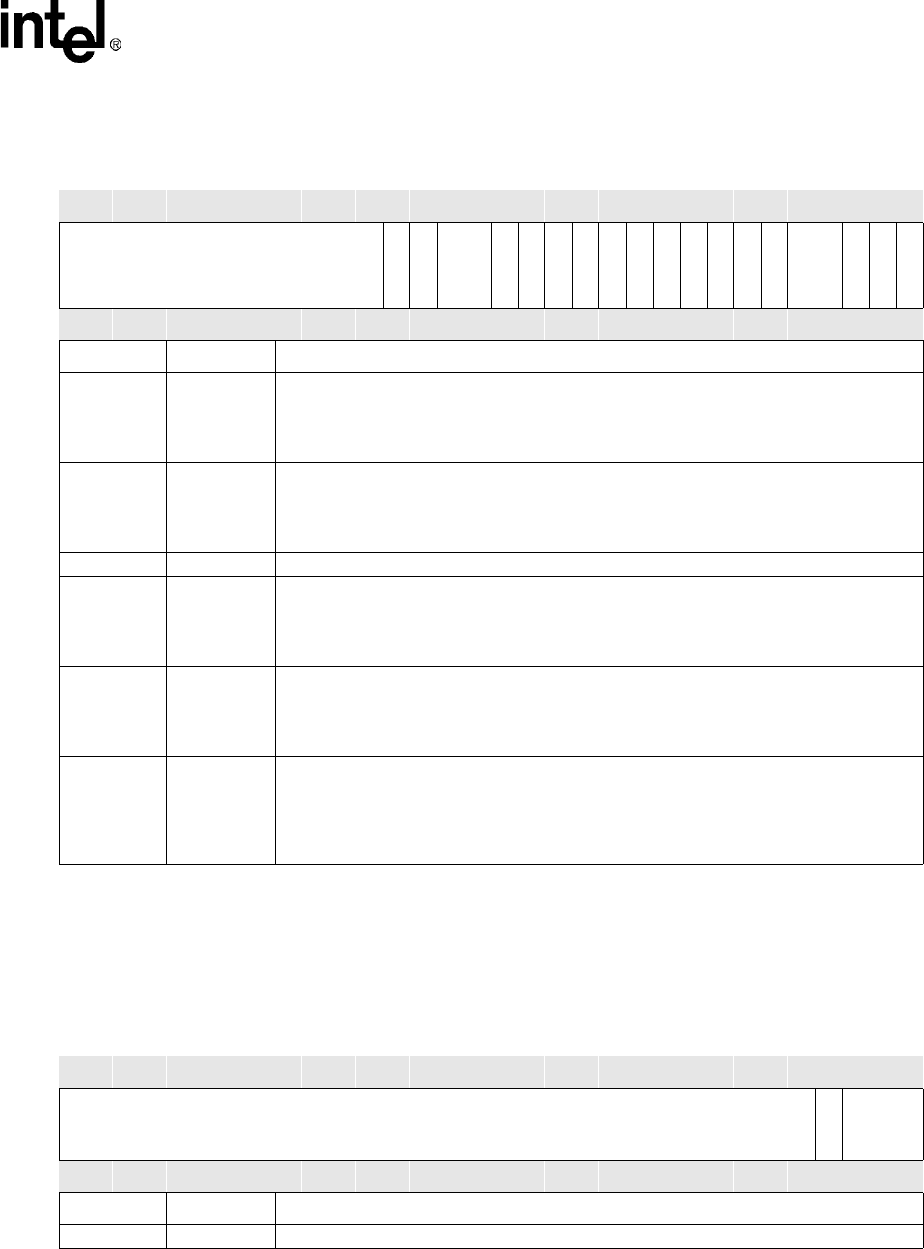

Table 13-9. POCR Bit Definitions (Sheet 1 of 2)

Physical Address

4050_0000

POCR Register AC’97 Controller Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

FEIE

reserved

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:4 — reserved