Intel® PXA255 Processor Developer’s Manual 12-31

USB Device Controller

These are read/write registers. Ignore reads from reserved bits. Write zeros to reserved bits.

12.6.6 UDC Endpoint x Control/Status Register (UDCCS3/8/13)

USCCS3/8/13, shown in Table 12-17, contains 4 bits that are used to operate endpoint(x), an

Isochronous IN endpoint.

12.6.6.1 Transmit FIFO Service (TFS)

The transmit FIFO service bit is be set if one or fewer data packets remain in the transmit FIFO.

UDCCSx[TFS] is cleared when two complete data packets are in the FIFO. A complete packet of

data is signified by loading 256 bytes or by setting UDCCSx[TSP].

12.6.6.2 Transmit Packet Complete (TPC)

The the UDC sets transmit packet complete bit when an entire packet is sent to the host. When this

bit is set, the IRx bit in the appropriate UDC status/interrupt register is set if transmit interrupts are

enabled. This bit can be used to validate the other status/error bits in the endpoint(x) control/status

register. The UDCCSx[TPC] bit gets cleared by writing a one to it. This clears the interrupt source

for the IRx bit in the appropriate UDC status/interrupt register, but the IRx bit must also be cleared.

Setting this bit does not prevent the UDC from transmitting the next buffer. The UDC issues NAK

handshakes to all IN tokens if this bit is set and neither buffer has been triggered by writing

64 bytes or setting UDCCSx[TSP].

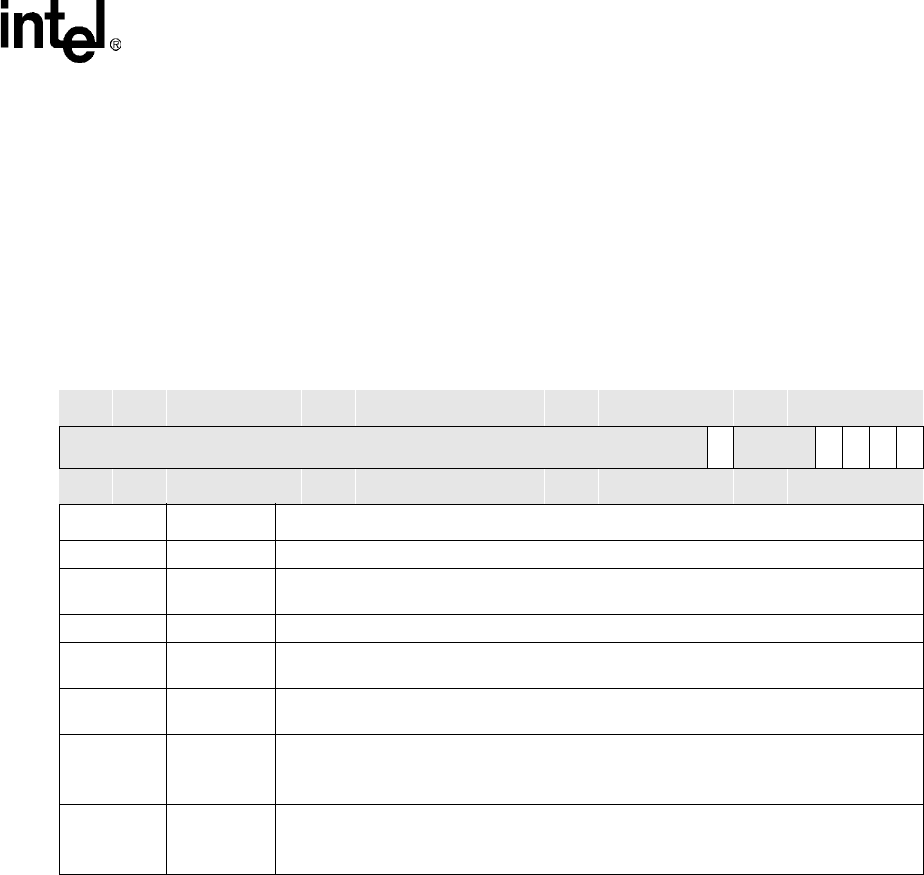

Table 12-17. UDCCS3/8/13 Bit Definitions

0x4060_001C

0x4060_0030

0x4060_0044

UDCCS3

UDCCS8

UDCC13

USB Device Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

TSP

reserved

TUR

FTF

TPC

TFS

Reset X X X X X X X X X X X X X X X X X X X X X X X X 0 0 0 0 0 0 0 1

Bit Name Description

31:8 — reserved

7TSP

Transmit short packet (read/write 1 to set).

1 = Short packet ready for transmission.

6:4 — reserved

3TUR

Transmit FIFO underrun (read/write 1 to clear)

1 = Transmit FIFO experienced an underrun.

2 FTF

Flush Tx FIFO (always read 0/ write a 1 to set)

1 = 1 – Flush Contents of TX FIFO

1TPC

Transmit packet complete (read/write 1 to clear).

0 = Error/status bits invalid.

1 = Transmit packet has been sent and error/status bits are valid.

0TFS

Transmit FIFO service (read-only).

0 = Transmit FIFO has no room for new data

1 = Transmit FIFO has room for at least 1 complete data packet