Intel® PXA255 Processor Developer’s Manual 2-15

System Architecture

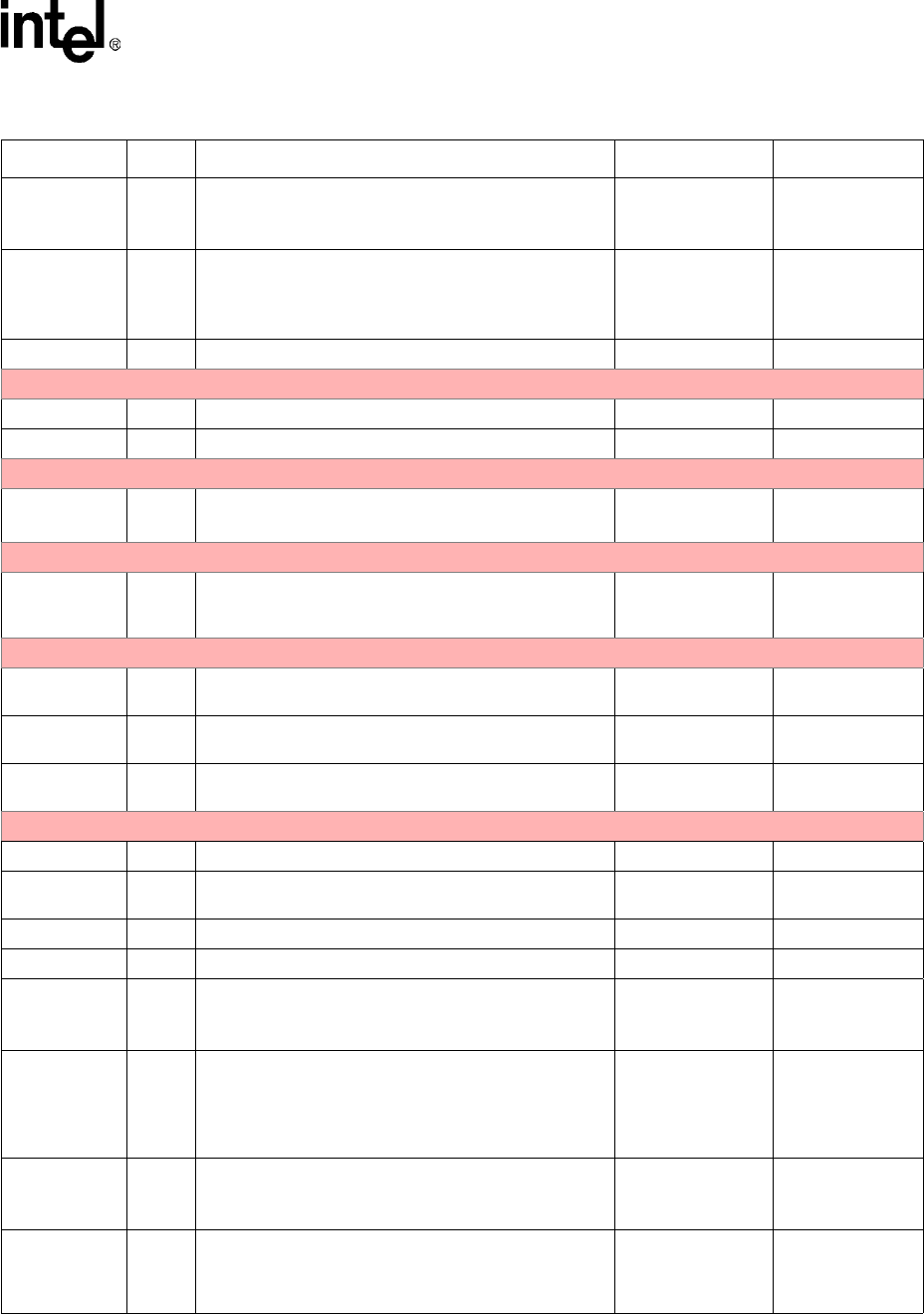

SDATA_OUT/

GPIO[30]

ICOCZ

AC97 Audio Port data out. (output) Output from the

PXA255 processor to Codecs 0 and 1.

I

2

S data out. (output) Output line for the I

2

S Controller.

Hi-Z - Note [1] Note [3]

SYNC/

GPIO[31]

ICOCZ

AC97 Audio Port sync signal. (output) Frame sync

signal for the AC97 Controller.

I

2

S sync. (output) Frame sync signal for the I

2

S

Controller.

Hi-Z - Note [1] Note [3]

nACRESET OC AC97 Audio Port reset signal. (output) Driven Low Driven Low

I

2

C Controller Pins

SCL ICOCZ I

2

C clock. (bidirectional) Hi-Z Hi-Z

SDA ICOCZ I

2

C data. (bidirectional). Hi-Z Hi-Z

PWM Pins

PWM[1:0]/

GPIO[17:16]

ICOCZ Pulse Width Modulation channels 0 and 1. (outputs) Hi-Z - Note [1] Note [3]

DMA Pins

DREQ[1:0]/

GPIO[19:20]

ICOCZ

DMA Request. (input) Notifies the DMA Controller that

an external device requires a DMA transaction. DREQ[1]

is GPIO[19]. DREQ[0] is GPIO[20].

Hi-Z - Note [1] Note [3]

GPIO Pins

GPIO[1:0] ICOCZ

General Purpose I/O. Wakeup sources on both rising

and falling edges on nRESET.

Hi-Z - Note [1] Note [3]

GPIO[14:2] ICOCZ

General Purpose I/O. More wakeup sources for sleep

mode.

Hi-Z - Note [1] Note [3]

GPIO[22:21] ICOCZ

General Purpose I/O. Additional General Purpose I/O

pins.

Hi-Z - Note [1] Note [3]

Crystal and Clock Pins

PXTAL IA 3.6864 Mhz crystal input. No external caps are required. Note [2] Note [2]

PEXTAL OA

3.6864 Mhz crystal output. No external caps are

required.

Note [2] Note [2]

TXTAL IA 32 Khz crystal input. No external caps are required. Note [2] Note [2]

TEXTAL OA 32 Khz crystal output. No external caps are required. Note [2] Note [2]

L_DD[12]/

GPIO[70]

ICOCZ

LCD display data. (output) Transfers pixel information

from the LCD Controller to the external LCD panel.

RTC clock. (output) Real time clock 1 Hz tick.

Hi-Z - Note [1] Note [3]

L_DD[13]/

GPIO[71]

ICOCZ

LCD display data. (output) Transfers the pixel

information from the LCD Controller to the external LCD

panel.

3.6864 MHz clock. (output) Output from 3.6864 MHz

oscillator.

Hi-Z - Note [1] Note [3]

L_DD[14]/

GPIO[72]

ICOCZ

LCD display data. (output) Transfers pixel information

from the LCD Controller to the external LCD panel.

32 kHz clock. (output) Output from the 32 kHz oscillator.

Hi-Z - Note [1] Note [3]

48MHz/GP[7] ICOCZ

48 MHz clock. (output) Peripheral clock output derived

from the PLL.

NOTE: This clock is only generated when the USB unit

clock enable is set.

Hi-Z - Note [1] Note [3]

Table 2-6. Pin & Signal Descriptions for the PXA255 Processor (Sheet 7 of 9)

Pin Name Type Signal Descriptions Reset State Sleep State