Intel® PXA255 Processor Developer’s Manual 9-9

I

2

C Bus Interface Unit

In master-transmit mode, if the target slave-receiver device cannot generate the acknowledge pulse,

the SDA line remains high. The lack of an acknowledge NAK causes the I

2

C unit to set the

ISR[BED] bit and generate the associated interrupt when enabled. The I

2

C unit automatically

generates a STOP condition and aborts the transaction.

In master-receive mode, the I

2

C unit sends a negative acknowledge (NAK) to signal the slave-

transmitter to stop sending data. The ICR[ACKNAK] bit controls the ACK/NAK bit value that the

I

2

C bus drives. As required by the I

2

C bus protocol, the ISR[BED] bit is not set for a master-

receive mode NAK. The I

2

C unit automatically transmits the ACK pulse after it receives each byte

from the serial bus. Before the unit receives the last byte, software must set the ICR[ACKNAK] bit

to 1 (NAK). The NAK pulse is sent after the last byte to indicate that the last byte has been sent.

In slave mode, the I

2

C unit automatically acknowledges its own slave address, independent of the

value in the ICR[ACKNAK] bit. In slave-receive mode, an ACK response automatically follows a

data byte, independent of the value in the ICR[ACKNAK] bit. The I

2

C unit sends the ACK value

after it receives the eighth data bit in a byte.

In slave-transmit mode, the I

2

C unit receives a NAK from the master to indicate the last byte has

been transferred. The master then sends a STOP or repeated START. The ISR[UB] bit remains set

until a STOP or repeated START is received.

9.4.4 Arbitration

The I

2

C bus’ multi-master capabilities require I

2

C bus arbitration. Arbitration takes place when

two or more masters generate a START condition in the minimum hold time.

Arbitration can take a long time. If the address bit and the R/nW are the same, the arbitration

scheme considers the data. Because the I

2

C bus has a wired-AND nature, a transfer does not lose

data if multiple masters signal the same bus states. If the address and the R/nW bit or the data they

contain are different, the master signals a high state loses arbitration and shuts off its data drivers. If

the I

2

C unit loses arbitration, it shuts off the SDA or SCL drivers for the rest of the byte transfer,

sets the ISR[ALD] bit, and returns to slave-receive mode.

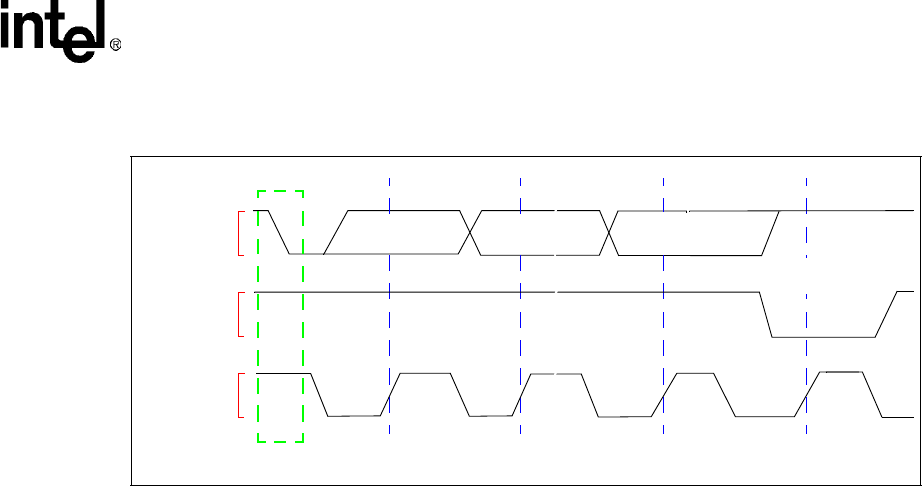

Figure 9-5. Acknowledge on the I

2

C Bus

1

2-7

8

9

SCL from

Master

Data Output

by Receiver

Data Output

by Transmitter

Clock Pulse

for Acknowledge

SDA released

SDA pulled low

by Receiver (ACK)

Start Condition

∼

∼

∼

∼

∼

∼

∼

∼

(SDA)

(SDA)