3-36 Intel® PXA255 Processor Developer’s Manual

Clocks and Power Manager

3.6.2 Clock Enable Register (CKEN)

CKEN, shown in Table 3-21, enables or disables the clocks to most of the peripheral units. For

lowest power consumption, the clock to any unit that is not being used must be disabled by writing

a zero to the appropriate bit.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

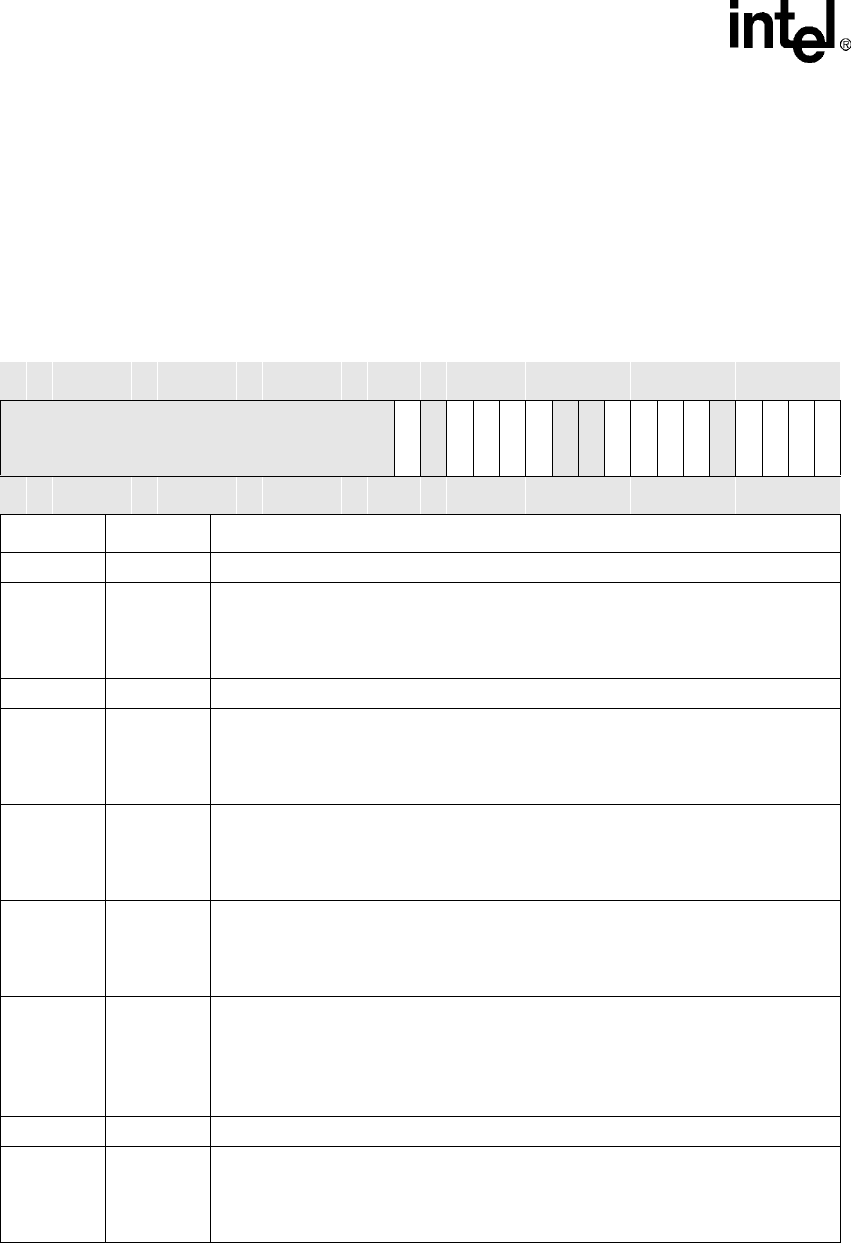

Table 3-21. CKEN Bit Definitions (Sheet 1 of 2)

0x4130_0004 CKEN Clocks Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

CKEN16

reserved

CKEN14

CKEN13

CKEN12

CKEN11

reserved

reserved

CKEN8

CKEN7

CKEN6

CKEN5

reserved

CKEN3

CKEN2

CKEN1

CKEN0

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 1 1 1 1 1 0 1 1 1 1 0 1 1 1 1

Bits Name Description

[31:17] — reserved

16 CKEN16

LCD Unit Clock Enable

0 – Clock to the unit is disabled

1 – Clock to the unit is enabled.

Set by hardware and watchdog resets

15 — reserved

14 CKEN14

I2C Unit Clock Enable

0 – Clock to the unit is disabled

1 – Clock to the unit is enabled.

Set by hardware and watchdog resets

13 CKEN13

FICP Unit Clock Enable

0 – Clock to the unit is disabled

1 – Clock to the unit is enabled.

These bits are set by hardware reset or watchdog reset

12 CKEN12

MMC Unit Clock Enable

0 – Clock to the unit is disabled

1 – Clock to the unit is enabled.

These bits are set by hardware reset or watchdog reset

11 CKEN11

USB Unit Clock Enable

0 – Clock to the unit is disabled

1 – Clock to the unit is enabled.

Set by hardware and watchdog resets

This bit must be set to allow the 48Mhz clock output on GP7 Alternate Function 1.

10 — reserved

9CKEN9

NSSP Unit Clock Enable

0 – Clock to the unit is disabled

1 – Clock to the unit is enabled.

Set by hardware and watchdog resets