4-28 Intel® PXA255 Processor Developer’s Manual

System Integration Unit

Several units have more than one source per interrupt signal. When an interrupt is signalled from

one of these units, the interrupt handler routine identifies which interrupt was signalled using the

interrupt controller’s pending register. This identifies the unit that made the request, but not the

exact source. The handler then reads the interrupting unit’s status register to identify which source

within the unit signalled the interrupt. For all interrupts that have one corresponding source, the

interrupt handler routine needs to use only the interrupt controller’s registers to identify the exact

cause of the interrupt. ICPR[16:15] and ICPR[7:0] are reserved bits and must be written as zeros.

Reads to these bits must be ignored.

4.3 Real-Time Clock (RTC)

Use the RTC to configure a clock source with a wide range of frequencies. Typically, the RTC is set

to be a 1 Hz output and is utilized as a system time keeper. There is also an alarm feature that

enables an interrupt or a wake up event when the RTC output clock increments to a pre-set value.

4.3.1 Real-Time Clock Operation

The RTC provides a general-purpose real-time reference for your design. The RTC Counter

register (RCNR) is initialized to zero after a hardware reset or a watchdog reset. It is a free running

counter that starts incrementing the count value after the deassertion of reset.

The counter is

incremented one 32kHz cycle after the rising edge of the Hz clock. Since the high phase of the 1 Hz

clock is one 32kHz cycle wide, it appears to increment on the falling edge of the 1 Hz clock.

Set

this counter to the desired value. If the counter is set to a value other than zero, write the desired

value to the RCNR. The value of the counter is unaffected by transitions into and out of Sleep or

Idle mode.

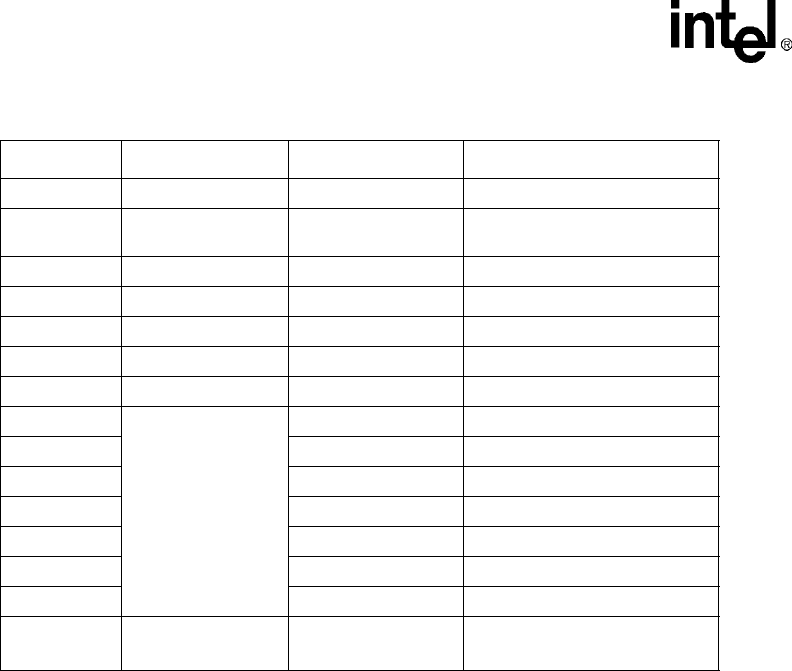

IS<13> I2S 5 I2S interrupt

IS<12> Core 1

PMU (Performance Monitor)

interrupt

IS<11> USB 7 USB interrupt

IS<10> 79 “OR” of GPIO edge detects 80-2

IS<9> 1 GPIO<1> edge detect

IS<8> 1 GPIO<0> edge detect

IS<7> Hardware UART 7 Hardware UART service request

IS<6> reserved

IS<5> reserved

IS<4> reserved

IS<3> reserved

IS<2> reserved

IS<1> reserved

IS<0> reserved

Total level 2 interrupt

sources

179

Table 4-36. List of First–Level Interrupts (Sheet 2 of 2)

Bit Position Source Unit # of Level 2 Sources Bit Field Description