9-4 Intel® PXA255 Processor Developer’s Manual

I

2

C Bus Interface Unit

When the I

2

C unit receives an address that matches the 7-bit address found in the I

2

C Slave

Address Register (ISAR) or the general call address (see Section 9.4.7), the interface either

remains in slave-receive mode or transitions to slave-transmit mode. The Read/Write bit (R/nW)

determines which mode the interface enters. The R/nW bit is the least significant bit of the byte

containing the slave address. If the R/nW bit is low, the master that initiated the transaction intends

write data and the I

2

C unit remains in slave-receive mode. If the R/nW is high, the master that

initiated the transaction intends to read data and the I

2

C unit transitions to slave-transmit mode.

Section 9.4.6 further defines slave operation.

When the I

2

C unit initiates a read or write on the I

2

C bus, it transitions from the default slave-

receive mode to the master-transmit mode. If the transaction is a write, the I

2

C unit remains in

master-transmit mode after the address transfer is completed. If the transaction is a read, the I

2

C

unit transmits the start address, then transitions to master-receive mode. Section 9.4.5 further

defines master operation.

9.3.3 Start and Stop Bus States

The I

2

C bus specification defines a transaction START, used at the beginning of a transfer, and a

transaction STOP bus state, used at the end of a transfer. A START condition occurs if a high to

low transition takes place on the SDA line when SCL is high. A STOP condition occurs if a low to

high transition takes place on the SDA line when SCL is high.

The I

2

C unit uses the ICR[START] and ICR[STOP] bits to:

• Initiate an additional byte transfer

• Initiate a START condition on the I

2

C bus

• Enable Data Chaining (repeated START)

• Initiate a STOP condition on the I

2

C bus

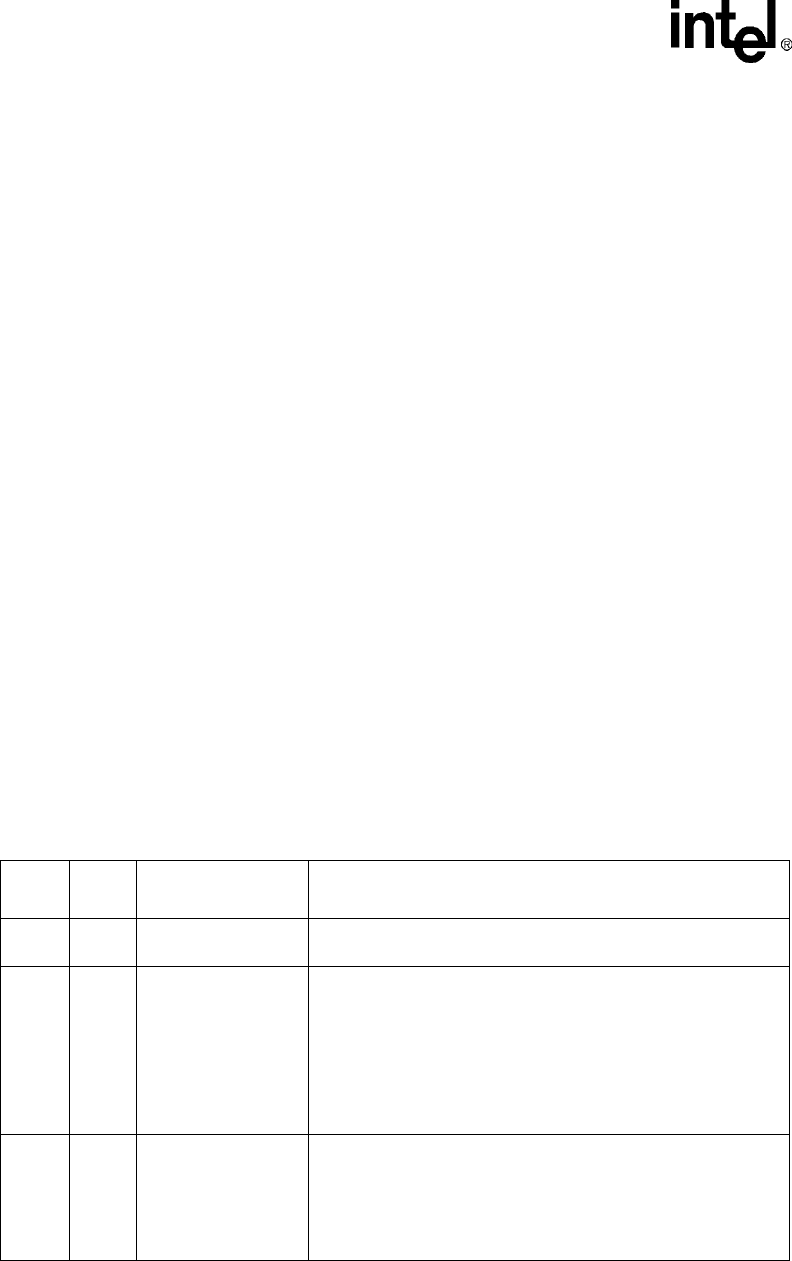

Table 9-4 defines the START and STOP bits in the ICR.

Table 9-4. START and STOP Bit Definitions

STOP

bit

STAR

T bit

Condition Notes

0 0 No START or STOP

I

2

C unit sends a no START or STOP condition. Used when

multiple data bytes need to be transferred.

01

START Condition and

Repeated START

I

2

C unit sends a START condition and transmit the 8-bit IDBR’s

contents. The IDBR must contain the 7-bit address and the R/nW

bit before a START is initiated.

For a Repeated Start, the IDBR contains the target slave address

and the R/nW bit. This allows a master to make multiple transfers

to different slaves without giving up the bus.

The interface stays in master-transmit mode for writes and

transitions to master-receive mode for reads.

1 X STOP Condition

In master-transmit mode, the I

2

C unit transmits the 8-bit IDBR and

sends a STOP condition on the I

2

C bus.

In master-receive mode, the ICR[ACKNAK] must be changed to a

negative ACK (see Section 9.4.3). The I

2

C unit transmits the NAK

bit, receives the data byte in the IDBR, and sends a STOP

condition on the I

2

C bus.