Intel® PXA255 Processor Developer’s Manual 5-19

DMA Controller

3STOPSTATE

Stop State (read-only).

0 – channel is running

1 – channel is in uninitialized or stopped state.

If the channel is in the uninitialized or stopped state, this status bit is set. If the

DCSR[STOPIRQEN] is set to 1, the DMAC generates an interrupt. Channel States are

described in Section 5.1.5.

Software must reprogram the DDADRx and write a 1 to the DCSR[RUN] bit to restart the

channel and clear this bit.

Software must write a 0 to the DCSR[STOPIRQEN] bit to reset the interrupt

2ENDINTR

End Interrupt (read / write).

0 – no interrupt

1 – interrupt caused because the current transaction was successfully completed and

DCMD[LENGTH] = 0.

DCMD[ENDIRQEN] bit must be set for an interrupt to occur. Software must write a 1 to this

bit to reset the corresponding interrupt. Writing a 0 to this bit has no effect.

1STARTINTR

Start Interrupt (read / write).

0 – no interrupt

1 – interrupt caused due to successful descriptor fetch

DCMD[STARTIRQEN] bit must be set for an interrupt to occur. Software must write a 1 to

this bit to reset the corresponding interrupt. Writing a 0 to this bit has no effect.

0

BUSERR

INTR

Bus Error Interrupt (read / write).

0 – no interrupt

1 – bus error caused interrupt

Indicates that there was an error while transferring data. An error during data transfer

occurs when the channel has a bad descriptor, source, or target address. An address is

considered bad when it points to a non-busable location or reserved space. Software must

write a 1 to this bit to reset the corresponding interrupt. Writing a 0 to this bit has no effect.

Only one error incidence per channel is logged. The channel that caused the error is

updated at the end of the transfer and is accessible after it logs an error until it is

reprogrammed and the corresponding run bit is set.

Table 5-7. DCSRx Bit Definitions (Sheet 2 of 2)

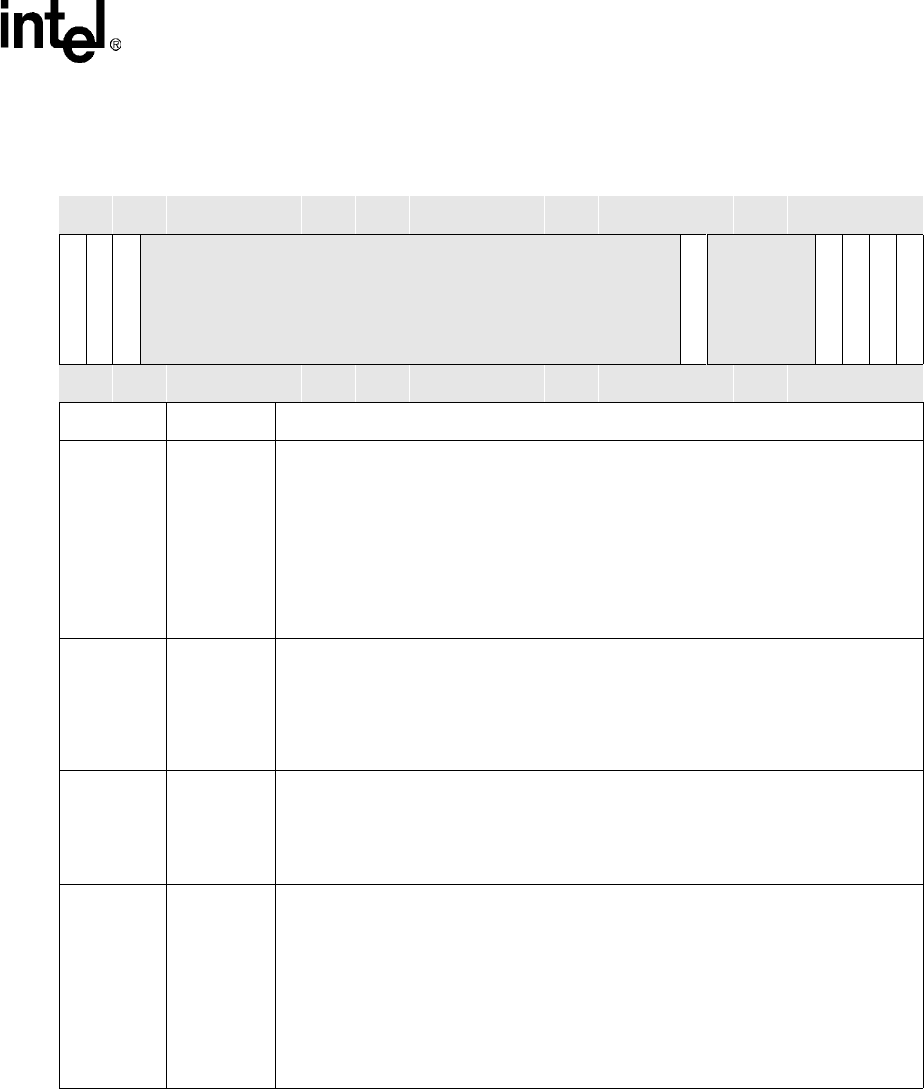

Physical Address

0x4000_0000 - 0x4000_003C

DMA Channel Control/Status

Register (DCSRx)

DMA Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RUN

NODESCFETCH

STOPIRQEN

reserved

REQPEND

reserved

STOPSTATE

ENDINTR

STARTINTR

BUSERRINTR

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0

Bits Name Description