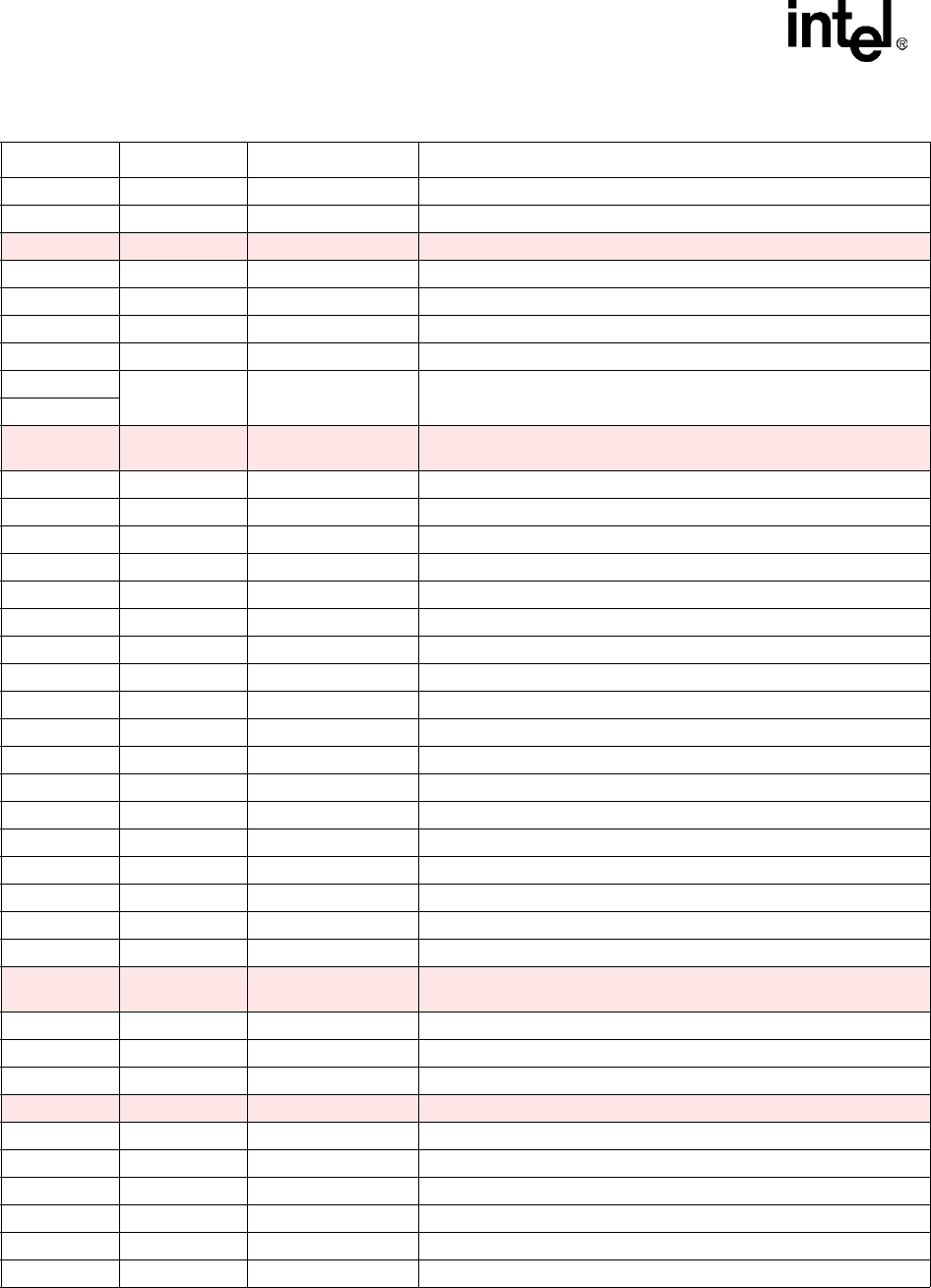

2-30 Intel® PXA255 Processor Developer’s Manual

System Architecture

0x40F0_002C — Reserved

0x40F0_0030 RCSR Reset Controller Status Register

SSP 0x4100_0000

0x4100_0000 SSCR0 SSP Control Register 0

0x4100_0004 SSCR1 SSP Control Register 1

0x4100_0008 SSSR SSP Status Register

0x4100_000C SSITR SSP Interrupt Test Register

0x4100_0010 SSDR (Write / Read) SSP Data Write Register/SSP Data Read Register

MMC

Controller

0x4110_0000

0x4110_0000 MMC_STRPCL Control to start and stop MMC clock

0x4110_0004 MMC_STAT MMC Status Register (read only)

0x4110_0008 MMC_CLKRT MMC clock rate

0x4110_000C MMC_SPI SPI mode control bits

0x4110_0010 MMC_CMDAT Command/response/data sequence control

0x4110_0014 MMC_RESTO Expected response time out

0x4110_0018 MMC_RDTO Expected data read time out

0x4110_001C MMC_BLKLEN Block length of data transaction

0x4110_0020 MMC_NOB Number of blocks, for block mode

0x4110_0024 MMC_PRTBUF Partial MMC TXFIFO FIFO written

0x4110_0028 MMC_I_MASK Interrupt Mask

0x4110_002C MMC_I_REG Interrupt Register (read only)

0x4110_0030 MMC_CMD Index of current command

0x4110_0034 MMC_ARGH MSW part of the current command argument

0x4110_0038 MMC_ARGL LSW part of the current command argument

0x4110_003C MMC_RES Response FIFO (read only)

0x4110_0040 MMC_RXFIFO Receive FIFO (read only)

0x4110_0044 MMC_TXFIFO Transmit FIFO (write only)

Clocks

Manager

0x4130_0000

0x4130_0000 CCCR Core Clock Configuration Register

0x4130_0004 CKEN Clock Enable Register

0x4130_0008 OSCC Oscillator Configuration Register

Network SSP 0x4140_0000

0x4140_0000 NSSCR0 NSSP Control Register 0

0x4140_0004 NSSCR1 NSSP Control Register 1

0x4140_0008 NSSSR NSSP Status Register

0x4140_000C NSSITR NSSP Interrupt Test Register

0x4140_0010 NSSDR NSSP Data Read/Write Register

0x4140_0028 NSSTO NSSP Time Out Register

Table 2-8. System Architecture Register Address Summary (Sheet 10 of 12)

Unit Address Register Symbol Register Description