Intel® PXA255 Processor Developer’s Manual 4-37

System Integration Unit

4.4.2.3 OS Timer Watchdog Match Enable Register (OWER)

The OWER, shown in Table 4-43, contains a single control bit (bit 0) that enables the watchdog

function. This bit is set by writing a one to it and can only be cleared by one of the reset functions

such as, hardware reset, sleep reset, watchdog reset, and GPIO reset.

4.4.2.4 OS Timer Count Register (OSCR)

The OSCR, shown in Table 4-44, is a 32-bit counter that increments on rising edges of the

3.6864 MHz clock. This counter can be read or written at any time. It is recommended that the

system write-protect this register through the MMU protection mechanisms.

After the OSCR is written, there is a delay before the register is actually updated. Software must

make sure the register has changed to the new value before relying on the contents of the register.

4.4.2.5 OS Timer Status Register (OSSR)

The OSSR, shown in Table 4-45, contains status bits that indicate a match has occurred between

any of the four match registers and the OSCR. These bits are set when the match event occurs

(following the rising edge of the 3.6864 MHz clock) and the corresponding interrupt enable bit is

set in the OIER. The OSSR bits are cleared by writing a one to the proper bit position. Writing

zeros to this register has no effect. Write all reserved bits as zeros and ignore all reads.

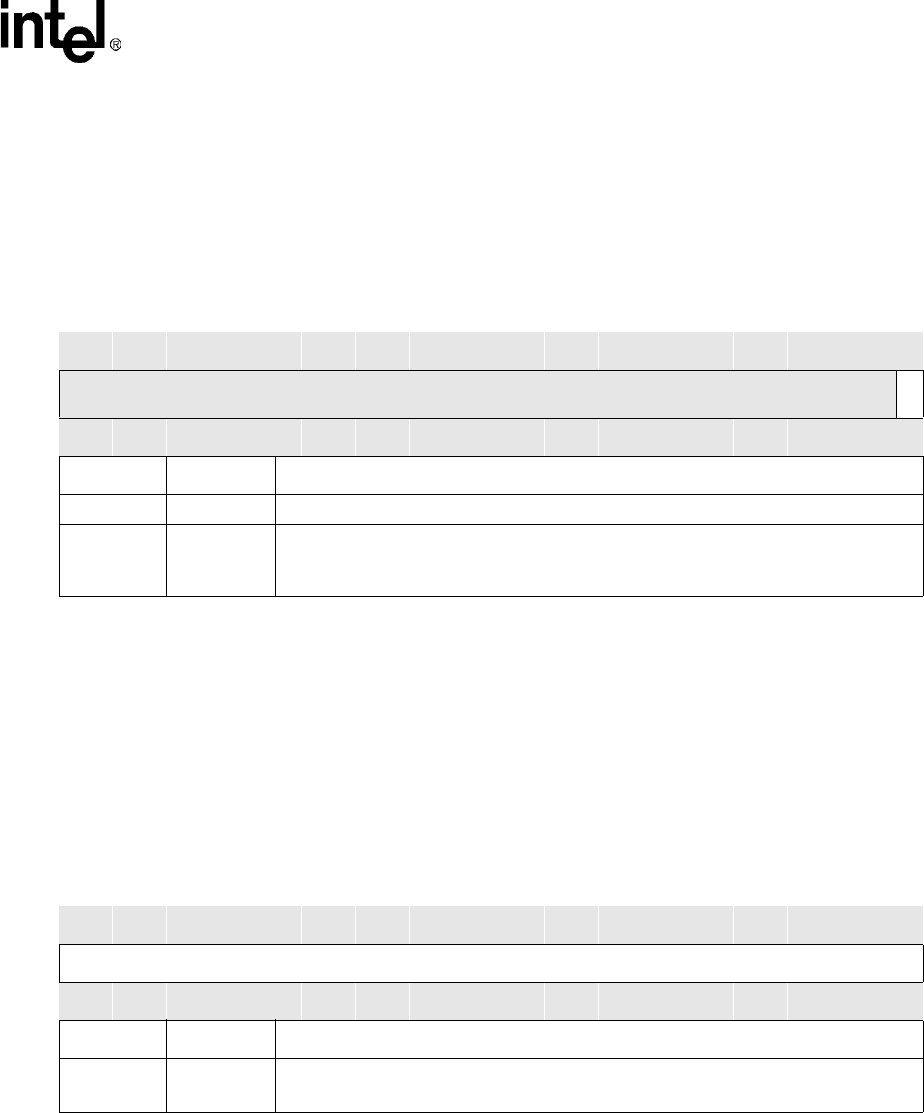

Table 4-43. OWER Bit Definitions

Physical Address

0x40A0_0018

OS Timer Watchdog Match Enable

Register (OWER)

System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

WME

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

<31:1> — reserved

<0> WME

Watchdog Match Enable

0 – OSMR3 match will NOT cause a reset of the processor

1 – OSMR3 match causes a reset of the processor.

Table 4-44. OSCR Bit Definitions

Physical Address

0x40A0_0010

OS Timer Count Register (OSCR) System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

OSCV

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

<31:0> OSCV

OS Timer Counter Value.

The current value of the OS timer counter.