6-66 Intel® PXA255 Processor Developer’s Manual

Memory Controller

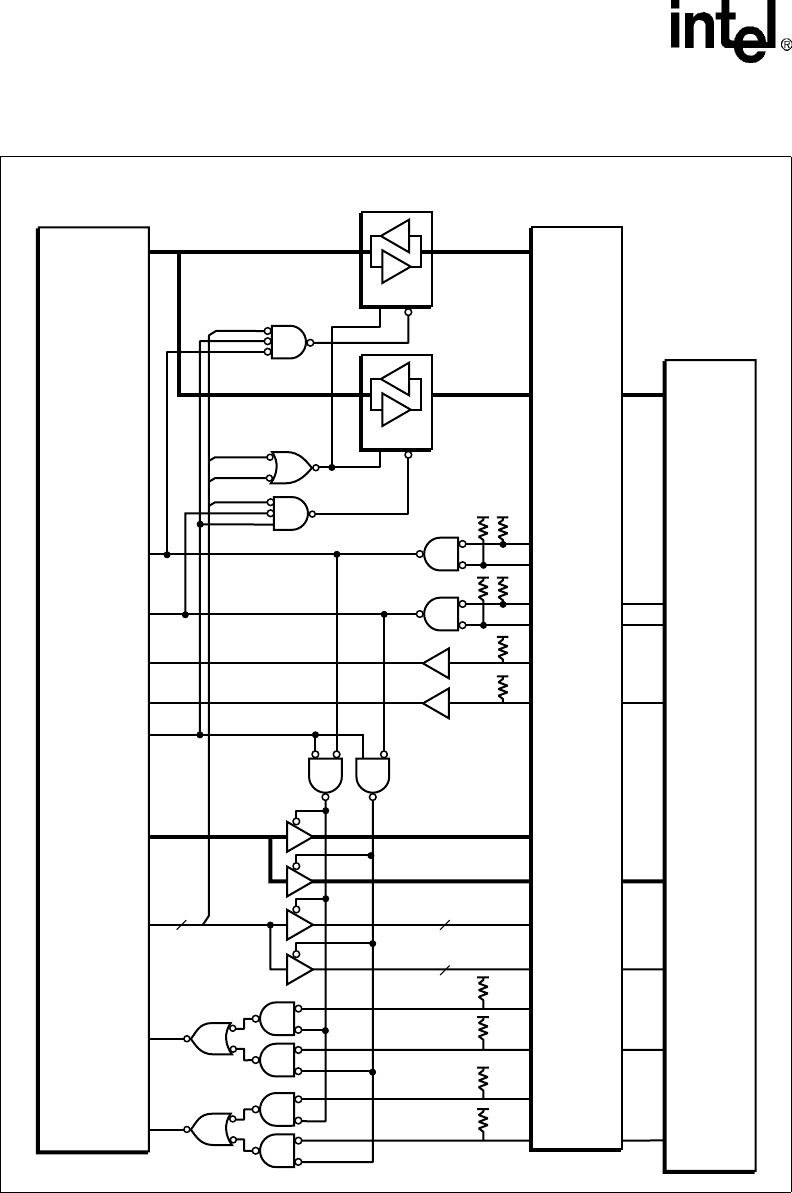

Figure 6-28. Expansion Card External Logic for a Two-Socket Configuration

D(15:0)

GPIO(w)

GPIO(x)

GPIO(y)

GPIO(z)

PSKTSEL

MA(25:0)

nPREG

nPWAIT

nPIOIS16

nPCE(1:2)

nPOE,

nPWE

nPIOW,

nPIOR

PXA255

Processor

D(15:0)

CD1#

CD2#

RDY/BSY#

WAIT#

WAIT#

IOIS1616#

A(25:0)

REG#

CE(1:2)#

OE#

WE#

IOR#

IOW#

Socket 0

D(15:0)

Socket 1

DIR

nPCEx

nPCEx

nPOE

nPIOR

OE#

DIR OE#

RDY/BSY#

CD1#

CD2#

A(25:0)

REG#

CE(1:2)#

OE#

WE#

IOR#

IOW#

IOIS1616#

WAIT#

6 6

6

WAIT#