12-44 Intel® PXA255 Processor Developer’s Manual

USB Device Controller

12.6.13.4 Isochronous Packet Error Endpoint 14 (IPE14)

The isochronous packet error for Endpoint 14 is set if Endpoint 14 is loaded with a data packet that

is corrupted.

This status bit is used in the interrupt generation of endpoint 14. To maintain

synchronization, software must monitor this bit when it services the SOF interrupt and reads the

frame number. This bit is not set if the token packet is corrupted or if the sync or PID fields of the

data packet are corrupted.

12.6.13.5 Start of Frame Interrupt Mask (SIM)

The UFNHR[SIM] bit is used to mask or enable the SOF interrupt request. When

UFNHR[SIM]=1, the interrupt is masked and the SIR bit is not allowed to be set. When

UFNHR[SIM]=0, the interrupt is enabled and when an interruptible condition occurs in the

receiver, the UFNHR[SIR] bit is set. Setting UFNHR[SIM] to a 1 does not affect the current state

of UFNHR[SIR]. It only blocks future zero to one transitions of UFNHR[SIR].

12.6.13.6 Start of Frame Interrupt Request (SIR)

The interrupt request bit is set if the UFNHR[SIM] bit is cleared and an SOF packet is received.

The UFNHR[SIR] bit is cleared by writing a 1 to it.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

12.6.14 UDC Frame Number Low Register (UFNLR)

UFNLR, shown in Table 12-25, is the eight least significant bits of the 11-bit frame number

contained in the last received SOF packet. The three remaining bits are located in the UFNHR.

This information is used for isochronous transfers. These bits are updated every SOF.

This is a read-only register. Ignore reads from reserved bits.

12.6.15 UDC Byte Count Register x (UBCR2/4/7/9/12/14)

UBCR2/4/7/9/12/14, shown in Table 12-26, maintains the remaining byte count in the active buffer

of OUT endpoint(x).

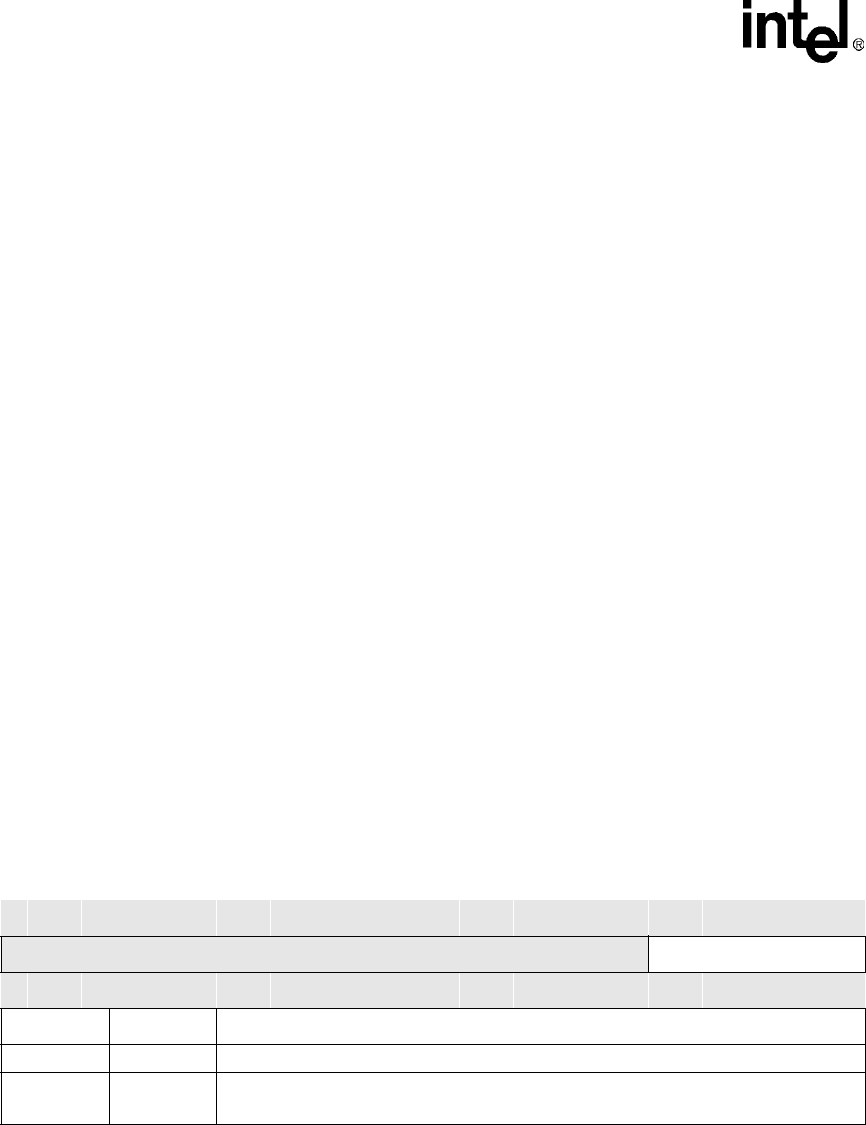

Table 12-25. UFNLR Bit Definitions

0x 4060_0064 UFNLR USB Device Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved 8-Bit Frame Number LSB

Reset X X X X X X X X X X X X X X X X X X X X X X X X 0 0 0 0 0 0 0 0

Bits Name Description

31:8 — reserved

7:0 FNLSB

Frame number LSB

Least significant 8-bits of frame number associated with last received SOF.