Intel® PXA255 Processor Developer’s Manual 16-13

Network SSP Serial Port

set) if the assertion of frame is not before the MSB is sent (For example, T5 <= T2 if

SSCR1[SFRMDIR] is set). Transmit Data transitions from the “End of Transfer Data State” to the

next MSB value upon the assertion of frame. The start delay field should be programmed to 0

whenever SSPSCLK or SSPSFRM is configured as an input.

16.4.4 Hi-Z on SSPTXD

The PXA255 processor NSSP supports placing SSPTXD into Hi-Z during idle times instead of

driving SSPTXD.

SSCR1[TTE] enables Hi-Z on SSPTXD. SSCR1[TTELP] controls when SSPTXD is placed into

Hi-Z.

16.4.4.1 TI Synchronous Serial Port

When SSCR1[TTE] is 0, the SSP behaves as described in Section 16.4.3.1.

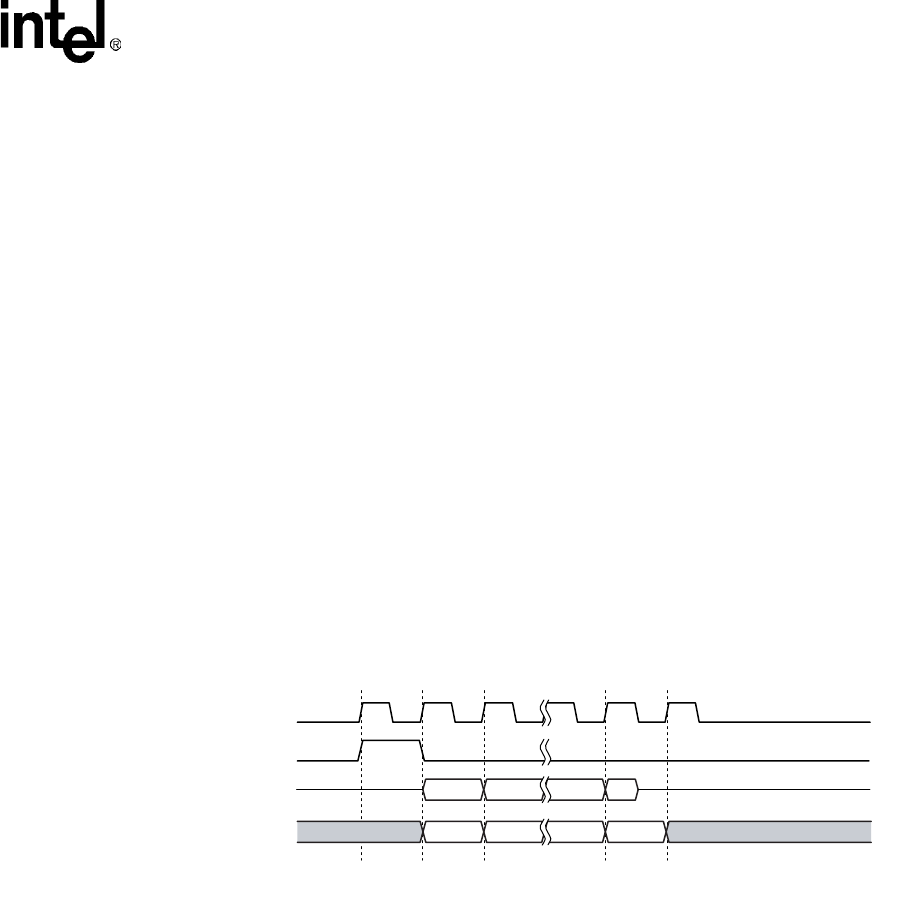

If SSCR1[TTE] is 1 and SSCR1[TTELP] is 0, SSPTXD is driven with the MSB at the first rising

edge of SSPSCLK after SSPSFRM is asserted. SSPTXD is Hi-Z after the falling edge of SSPSCLK

for the LSB (1 clock edge after the clock edge that starts the LSB). Figure 16-11shows the pin

timing for this mode.

If SSCR1[TTE] is 1 and SSCR1[TTELP] is 1, SSPTXD is driven with the MSB at the first rising

edge of SSPSCLK after SSPSFRM is asserted. SSPTXD is Hi-Z at the next rising edge of

SSPSCLK after the LSB (2 clock edges after the clock edge that starts the LSB). Figure 16-12

shows the pin timing for this mode.

Figure 16-11. TI SSP with SSCR[TTE]=1 and SSCR[TTELP]=0

A9974-01

SSPRXD

SSPSFRM

SSPSCLK

SSPTXD

MSB 4 to 32 Bits LSB

Bit[N] Bit[N-1] Bit[1] Bit[0]

Bit[N] Bit[N-1] Bit[1] Bit[0]

Undefined Undefined