Intel® PXA255 Processor Developer’s Manual 9-11

I

2

C Bus Interface Unit

If the I

2

C unit loses arbitration as the address bits are transferred and it is not addressed by the

address bits, the I

2

C unit resends the address when the I

2

C bus becomes free. A resend is possible

because the IDBR and ICR registers are not overwritten when arbitration is lost.

If the I

2

C unit loses arbitration because another bus master addresses the processor as a slave

device, the I

2

C unit switches to slave-receive mode and overwrites the original data in the I

2

C data

buffer register. Software can clear the start and re-initiate the master transaction.

Note: Software must prevent the I

2

C unit from starting a transaction to its own slave address because

such a transaction puts the I

2

C unit in an indeterminate state.

Arbitration has boundary conditions in case an arbitration process is interrupted by a repeated

START or STOP condition transmitted on the I

2

C bus. To prevent errors, the I

2

C unit acts as a

master if no arbitration takes place in the following circumstances:

• Between a repeated START condition and a data bit

• Between a data bit and a STOP condition

• Between a repeated START condition and a STOP condition

These situations occur if different masters write identical data to the same target slave

simultaneously and arbitration cannot be resolved after the first data byte transfer.

Note: Software ensures that arbitration is resolved quickly. For example, software can ensure that masters

send unique data by requiring that each master transmit its I

2

C address as the first data byte of any

transaction. When arbitration is resolved, the winning master sends a restart and begins a valid data

transfer. The slave discards the master’s address and use the other data.

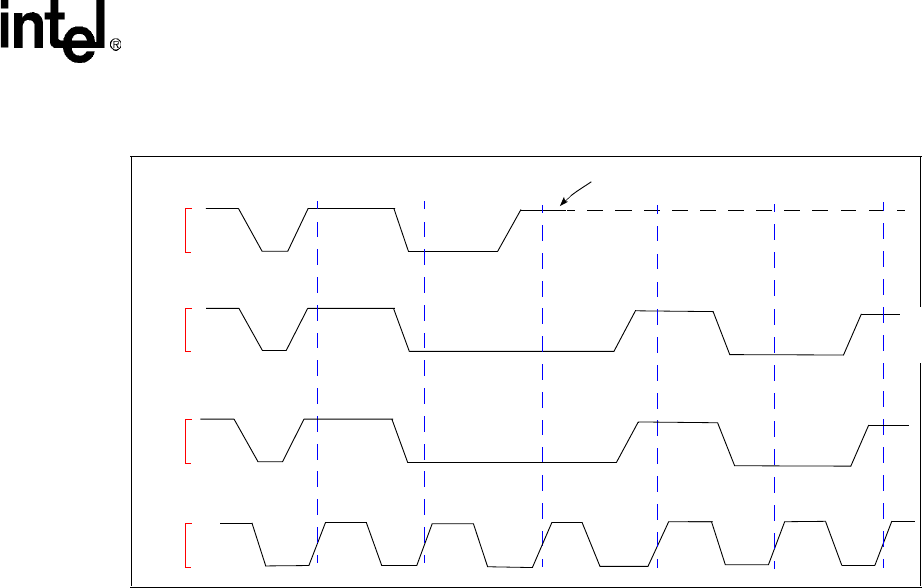

Figure 9-7. Arbitration Procedure of Two Masters

SDA

SCL

Data 1

Data 2

Transmitter 1 Leaves Arbitration

Data 1 SDA