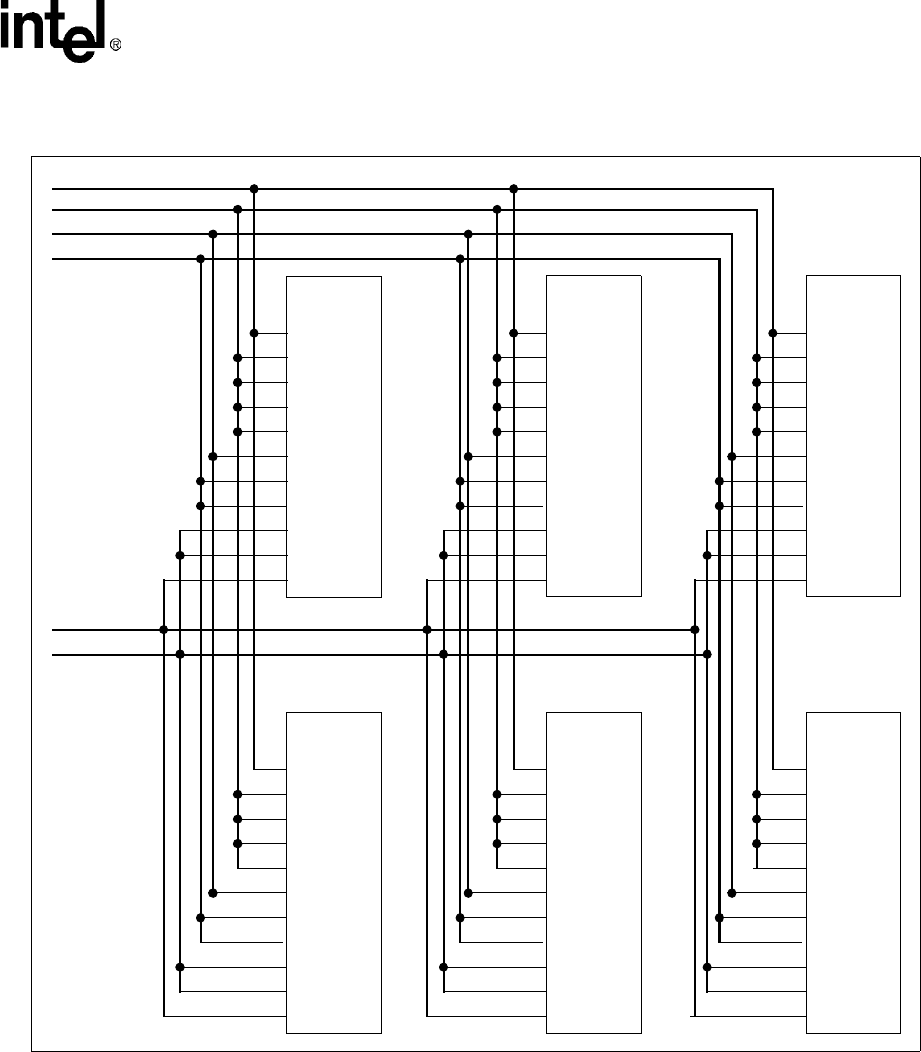

Intel® PXA255 Processor Developer’s Manual 6-5

Memory Controller

Figure 6-2. SDRAM Memory System Example

4Mx16

SDRAM

nCS

nRAS

nCAS

CLK

CKE

nWE

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

4Mx16

SDRAM

nCS

nRAS

nCAS

CLK

CKE

nWE

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

4Mx16

SDRAM

nCS

nRAS

nCAS

CLK

CKE

nWE

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

4Mx16

SDRAM

nCS

nRAS

nCAS

CLK

CKE

nWE

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

4Mx16

SDRAM

nCS

nRAS

nCAS

CLK

CKE

nWE

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

4Mx16

SDRAM

nCS

nRAS

nCAS

CLK

CKE

nWE

addr(11:0)

BA(1:0)

DQML

DQMH

DQ(15:0)

MD(31:0)

DQM(3:0)

MA(23:10)

SDCLK(2:1)

nSDRAS, nSDCAS, nWE, CKE(1)

nSDCS(2:0)

0

0

1

1

2

2

1

1

1

1

2

2

21:10

23:22

15:0

31:16

0

3

2

31:16

31:16

15:0

15:0

23:22

23:22

23:22

23:22

23:22

21:10

21:10

21:10

21:10 21:10

1

1

1

0

0

2

3

3

2