Intel® PXA255 Processor Developer’s Manual 6-25

Memory Controller

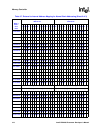

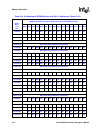

2x12x11x32 BA1 BA0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2x12x11x16 BA1 BA0 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2x13x8x32 BA1 BA0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2x13x8x16 BA1 BA0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2x13x9x32 BA1 BA0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2x13x9x16 BA1 BA0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2x13x10x32 NOT VALID (too big)

2x13x10x16 BA1 BA0 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

2x13x11x32 NOT VALID (too big)

2x13x11x16 NOT VALID (too big)

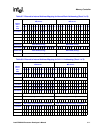

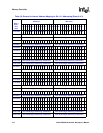

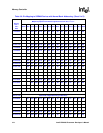

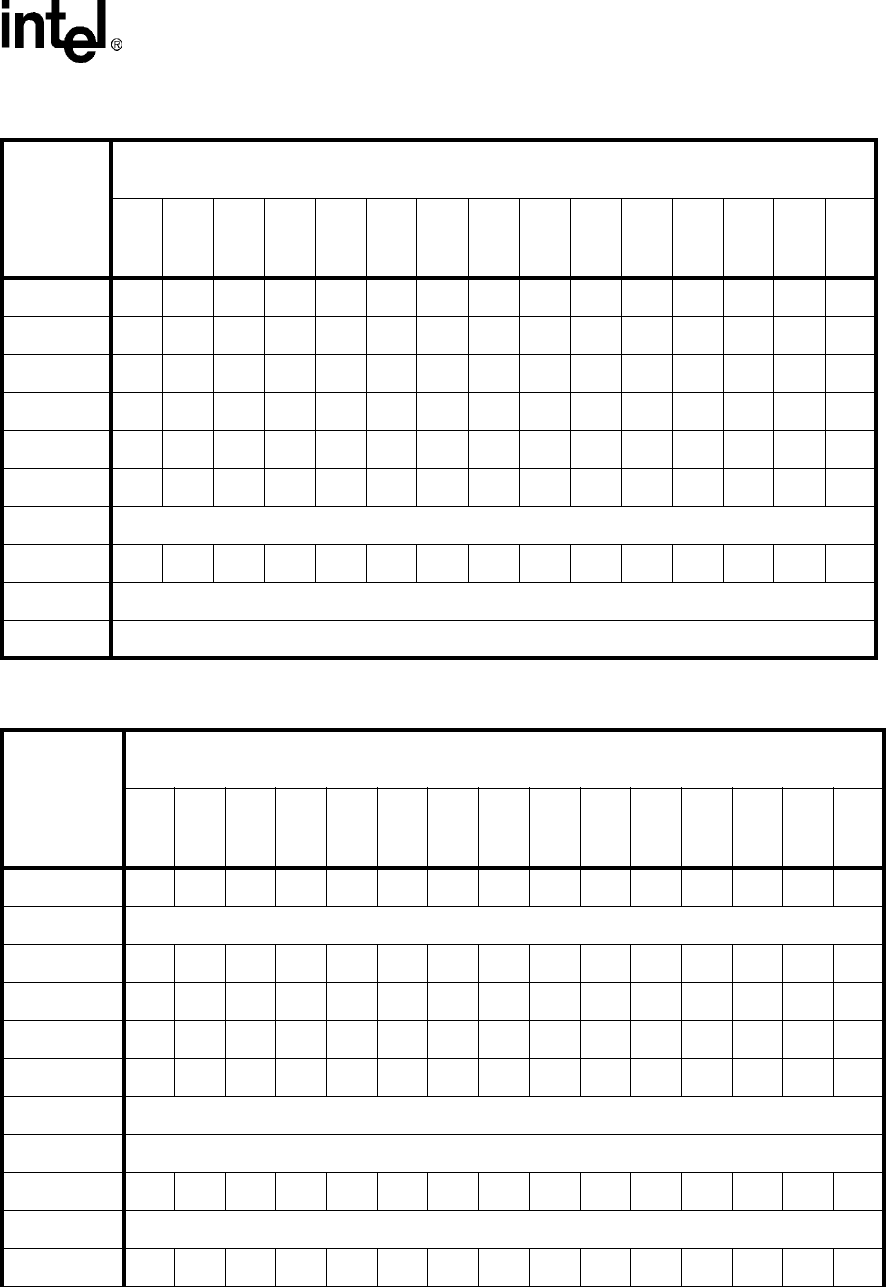

Table 6-10. Pin Mapping to SDRAM Devices with SA1111 Addressing (Sheet 1 of 3)

# Bits

Bank x

Row x

Col x

Data

Pin mapping to SDRAM devices for SA1111 Addressing Options.

MA[24:10] represent the address signals driven from the PXA255 processor.

MA24 MA23 MA22 MA21 MA20 MA19 MA18 MA17 MA16 MA15 MA14 MA13 MA12 MA11 MA10

1x11x8x32 BA0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x11x8x16 NOT VALID (illegal addressing combination)

1x11x9x32 BA0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x11x9x16 BA0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x11x10x32 BA0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x11x10x16 BA0 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

1x11x11x32 NOT VALID (illegal addressing combination)

1x11x11x16 NOT VALID (illegal addressing combination)

1x12x8x32 A11BA0A10A9A8A7A6A5A4A3A2A1A0

1x12x8x16 NOT VALID (illegal addressing combination)

1x12x9x32 A11BA0A10A9A8A7A6A5A4A3A2A1A0

Table 6-9. Pin Mapping to SDRAM Devices with Normal Bank Addressing (Sheet 3 of 3)

# Bits

Bank x

Row x

Col x

Data

Pin mapping to SDRAM devices for Normal Addressing.

MA[24:10] represent the address signals driven from the processor.

MA24 MA23 MA22 MA21 MA20 MA19 MA18 MA17 MA16 MA15 MA14 MA13 MA12 MA11 MA10