10-12 Intel® PXA255 Processor Developer’s Manual

UARTs

10.4.2.6 FIFO Control Register (FCR)

The FCR, shown in Table 10-11, is a write-only register that is located at the same address as the

IIR, which is a read-only register. The FCR enables/disables the transmitter/receiver FIFOs, clears

the transmitter/receiver FIFOs, and sets the receiver FIFO trigger level.

This is a write-only register. Write zeros to reserved bits.

1100

Second

Highest

Character

Timeout

Indication

FIFO mode only: At least

one character is in the

Receive FIFO and no data

has been sent for four

character times.

Reading the Receiver FIFO,

setting FCR[RESETRF] or

a new start bit is received

0010

Third

Highest

Transmit FIFO

Data Request

Non-FIFO mode: Transmit

Holding register empty

FIFO mode: Transmit has

half, or less than half, data

Non-FIFO mode: Reading

the IIR Register (if the

source of the interrupt) or

writing into the Transmit

Holding Register

FIFO mode: Reading the

IIR Register (if the source of

the interrupt) or writing to

the Transmitter FIFO

0000

Fourth

Highest

Modem Status

Clear to Send, Data Set

Ready, Ring Indicator, Data

Carrier Detect

Reading the Modem Status

Register

Table 10-10. Interrupt Identification Register Decode (Sheet 2 of 2)

Interrupt ID Bits Interrupt SET/RESET Function

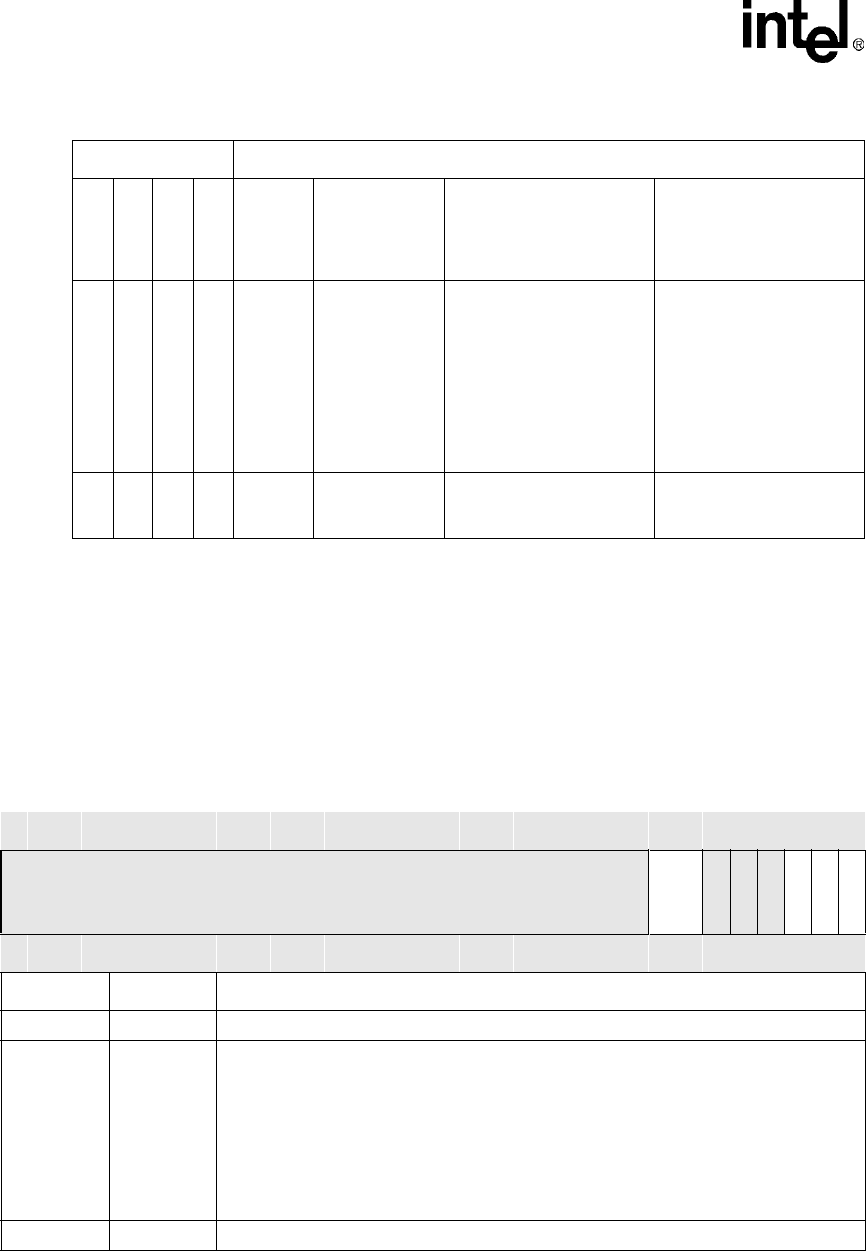

Table 10-11. FCR Bit Definitions (Sheet 1 of 2)

Base+0x08 FIFO Control Register UART

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

ITL

reserved

reserved

reserved

RESETTF

RESETRF

TRFIFOE

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:8 — reserved

7:6 ITL

Interrupt Trigger Level: When the number of bytes in the receiver FIFO equals the interrupt

trigger level programmed into this field and the Received Data Available Interrupt is

enabled via the IER, an interrupt is generated and appropriate bits are set in the IIR. The

receive DMA request is also generated when the trigger level is reached.

0b00 – 1 byte or more in FIFO causes interrupt (Not valid in DMA mode)

0b01 – 8 bytes or more in FIFO causes interrupt and DMA request

0b10 – 16 bytes or more in FIFO causes interrupt and DMA request

0b11 – 32 bytes or more in FIFO causes interrupt and DMA request

5:3 — reserved