16-6 Intel® PXA255 Processor Developer’s Manual

Network SSP Serial Port

16.4.3.2 SPI Protocol Details

The SPI protocol has four possible sub-modes, depending on the SSPSCLK edges selected for

driving data and sampling received data and on the selection of the phase mode of SSPSCLK (see

Section 16.4.3.2.1 for complete descriptions of each mode).

When the SSP is disabled or in idle mode, SSPSCLK and SSPTXD are low and SSPSFRM is high.

When transmit data is available to send, SSPSFRM goes low (one clock period before the first

rising edge of SSPSCLK) and stays low for the remainder of the frame. The most significant bit of

the serial data is driven onto SSPTXD one half-cycle later. Halfway into the first bit period,

SSPSCLK asserts high and continues toggling for the remaining data bits. Data transitions on the

falling edge of SSPSCLK. Four to 32 bits can be transferred per frame.

With the assertion of SSPSFRM, receive data is simultaneously driven from the peripheral on

SSPRXD, MSB first. Data transitions on SSPSCLK falling edges and is sampled by the controller

on rising edges. At the end of the frame, SSPSFRM is de-asserted high one clock period (one half

clock cycle after the last falling edge of SSPSCLK) after the last bit latched at its destination and

the completed incoming word is shifted into the incoming FIFO. The peripheral can drive

SSPRXD to a high-impedance state after sending the last bit of the frame. SSPTXD retains the last

value transmitted when the controller goes into idle mode, unless the SSP is disabled or reset

(which forces SSPTXD low).

For back-to-back transfers, frames start and complete similar to single transfers, except SSPSFRM

does not de-assert between words. Both transmitter and receiver are configured for the word length

and internally track the start and end of frames. There are no dead bits; the least significant bit of

one frame is followed immediately by the most significant bit of the next.

When using the SPI protocol, the SSP can either be a master or a slave device. However, the clock

and frame direction must be the same. For example, the SSCR1[SCLKDIR] and

SSCR0[SFRMDIR] must both be set or both be cleared.

Figure 16-3 shows when back-to-back frames are transmitted for the Motorola SPI* frame

protocol. Figure 16-4 shows one of the four possible configurations for the Motorola SPI* frame

protocol for a single transmitted frame.

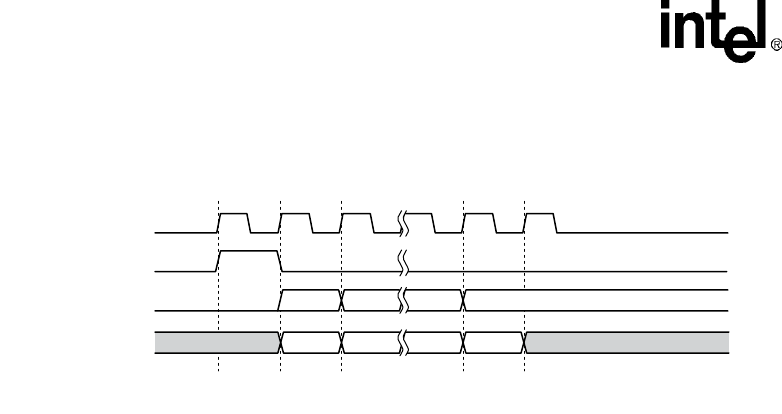

Figure 16-2. Texas Instruments Synchronous Serial Frame* Protocol (single transfers)

A9518-02

SSPRXD

SSPSFRM

SSPSCLK

SSPTXD

MSB 4 to 32 Bits LSB

Bit[N] Bit[N-1] Bit[1] Bit[0]

Bit[N] Bit[N-1] Bit[1] Bit[0]

Undefined Undefined