Intel® PXA255 Processor Developer’s Manual 6-47

Memory Controller

2:0 R/W RTx<2:0>

ROM type

000 - Nonburst ROM or Flash Memory

001 - SRAM

010 - Burst-of-four ROM or Flash (with non-burst writes)

011 - Burst-of-eight ROM or Flash (with non-burst writes)

100 - Variable Latency I/O (VLIO)

101 - reserved

110 - reserved

111 - reserved

Burst refers to the device’s timing. When the subsequent reads from the

device take less time than the first read from a device, it is referred to as

burst timing. The address bits must also be taken into account for burst

timing devices. For example, in a burst-of-four device, only the lower two

non-byte address bits can change for burst timing. For 32-bit devices, this is

MA[3:2]. The address order can go 00, 01, 10, 11 where the reads from 01,

10, and 11, take less time to come out of the device. For burst-of-eight

devices, the lower three non-byte address bits can change. Writes to these

devices are non-burst.

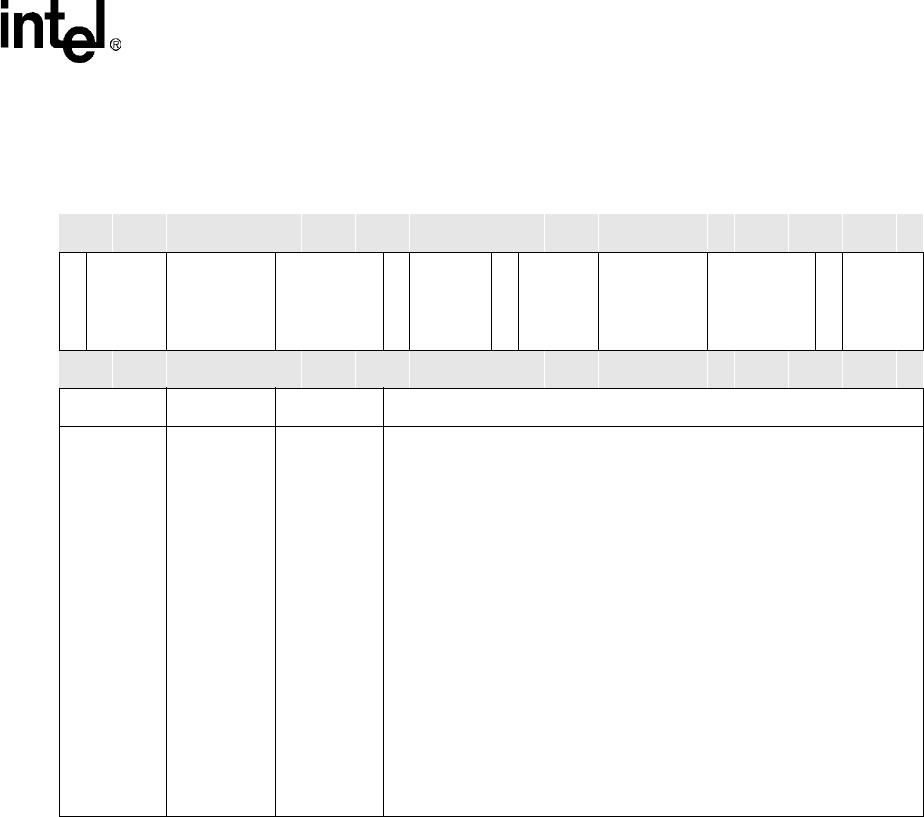

Table 6-21. MSC0/1/2 Bit Definitions (Sheet 3 of 3)

0x4800_0008

0x4800_000C

0x4800_0010

MSC0

MSC1

MSC2

Memory Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

RBUFF1/3/5

RRR1/3/5 RDN1/3/5 RDF1/3/5

RBW1/3/5

RT1/3/5

RBUFF0/2/4

RRR0/2/4

RDN0/2/4 RDF0/2/4

RBW0/2/4

RT0/2/4

Reset

0 1 1 1 1 1 1 1 1 1 1 1 0 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 * 0 0 0

Bits Access Name Description