Intel® PXA26x Processor Family Developer’s Manual 4-19

System Integration Unit

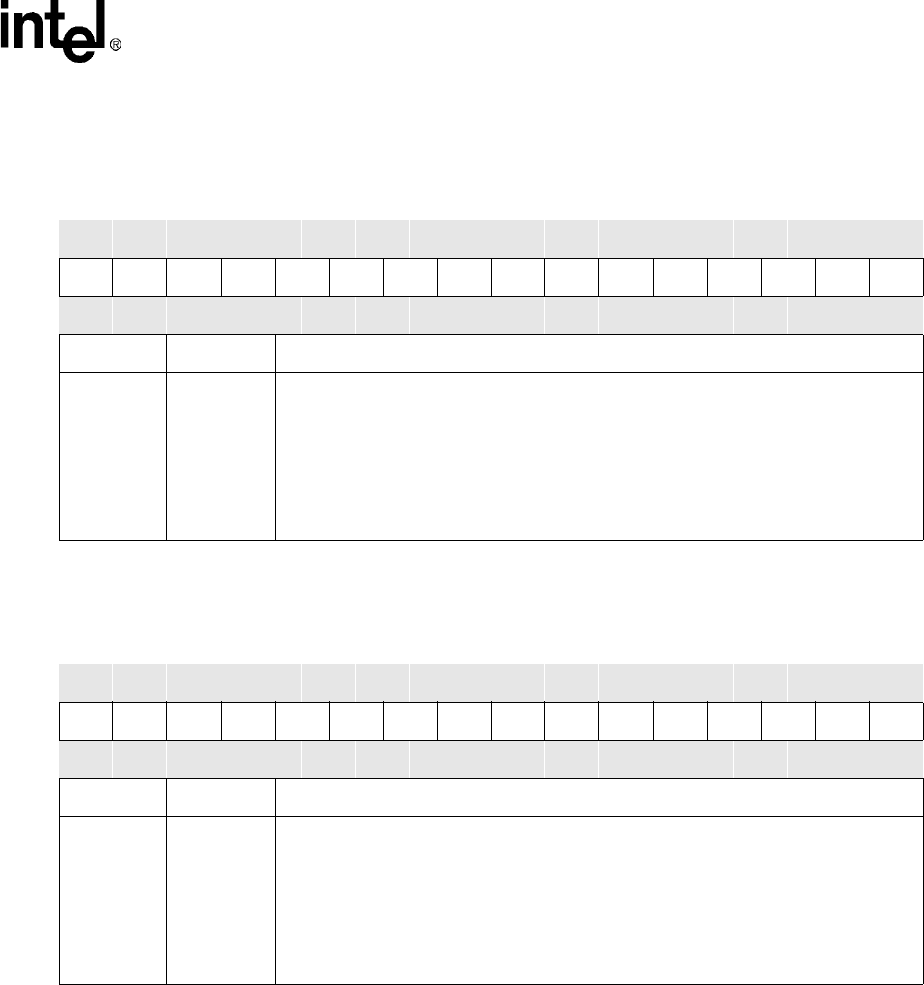

Table 4-26. GAFR1_L Bit Definitions

Physical Address

0x40E0_005C

GAFR1_L System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AF47 AF46 AF45 AF44 AF43 AF42 AF41 AF40 AF39 AF38 AF37 AF36 AF35 AF34 AF33 AF32

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

<31:0> AF[x]

GPIO PIN ‘X’ ALTERNATE FUNCTION SELECT BITS (where x = 32 through 47):

A bit-pair in this register determines the corresponding GPIO pin’s functionality as one of

the alternate functions that is mapped to it or as a generic GPIO pin.

00 – The corresponding GPIO pin (GPIO[x]) is used as a general purpose I/O.

01 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 1.

10 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 2.

11 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 3.

Table 4-27. GAFR1_U Bit Definitions

Physical Address

0x40E0_0060

GAFR1_U System Integration Unit

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

AF63 AF62 AF61 AF60 AF59 AF58 AF57 AF56 AF55 FA54 AF53 AF52 AF51 AF50 AF49 AF48

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

<31:0> AF[x]

GPIO PIN ‘X’ ALTERNATE FUNCTION SELECT BITS (where x = 48 through 63):

A bit-pair in this register determines the corresponding GPIO pin’s functionality as one of

the alternate functions that is mapped to it or as a generic GPIO pin.

00 – The corresponding GPIO pin (GPIO[x]) is used as a general purpose I/O.

01 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 1.

10 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 2.

11 – The corresponding GPIO pin (GPIO[x]) is used for its alternate function 3.