14-14 Intel® PXA26x Processor Family Developer’s Manual

Inter-Integrated Circuit Sound Controller

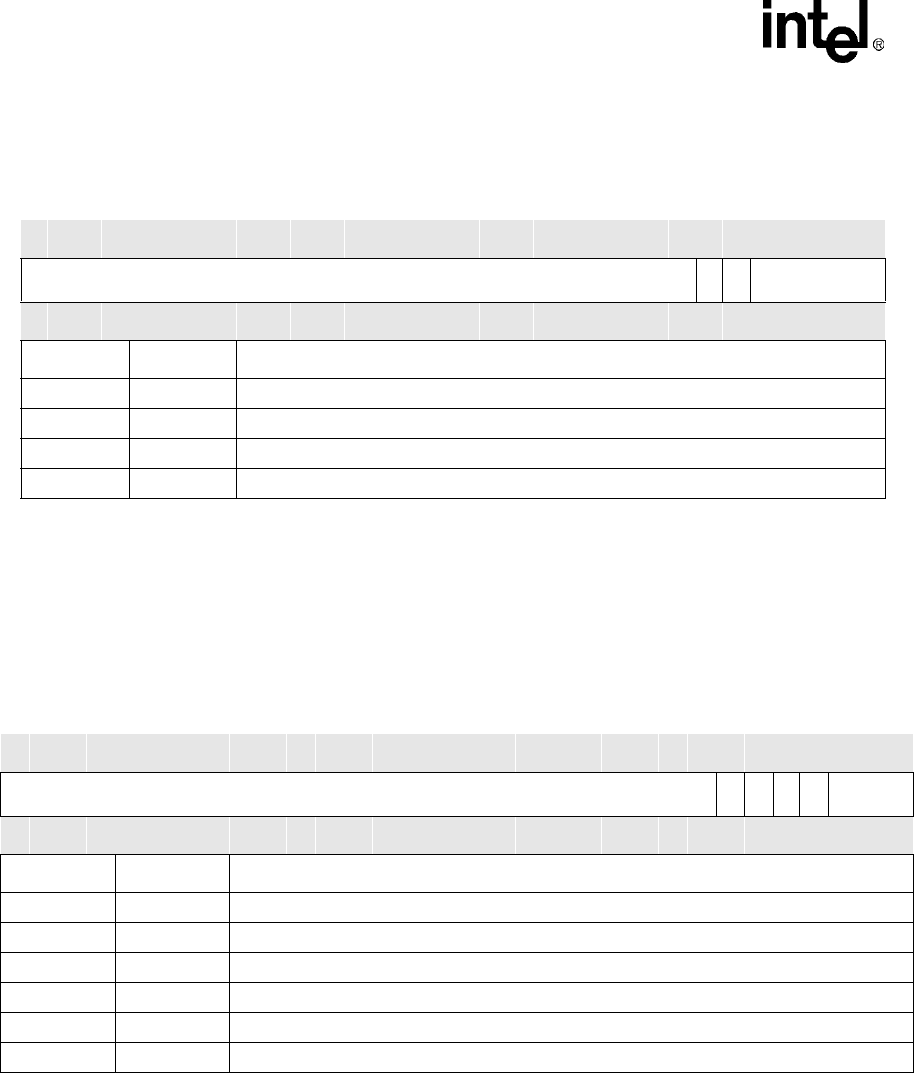

14.6.6 Serial Audio Interrupt Mask Register (SAIMR)

Writing a one to the corresponding bit position in the Interrupt Mask Register enables the

corresponding interrupt signal. All bits are read/write. Table 14-10 shows the bit layout of SAIMR.

14.6.7 Serial Audio Data Register (SADR)

Writing a 32-bit sample to this register updates the data into the transmit FIFO. Reading this

register flushes a 32-bit sample from the receive FIFO.

Table 14-11 shows the bit layout of SADR. Figure 14-3 illustrates data flow through the FIFOs and

SADR.

Table 14-9. SAICR Bit Descriptions

Physical Address

0x4040-0018

Serial Audio Interrupt Clear

Register

I

2

S Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

ROR

TUR

Reserved

Reset

r r r r r r r r r r r r r r r r r r r r r r r r r r r r r r r r

Bits Name Description

31:7 — Reserved

6 ROR Clear receive FIFO overrun interrupt and ROR status bit in SASR0.

5 TUR Clear transmit FIFO under-run interrupt and TUR status bit in SASR0.

4:0 — Reserved

Table 14-10. SAIMR Bit Descriptions

Physical Address

0x4040-0014

Serial Audio Interrupt Mask Register I

2

S Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

ROR

TUR

RFS

TFS

Reserved

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:7 — Reserved

6 ROR Enable receive FIFO overrun condition based interrupt.

5 TUR Enable FIFO under-run condition based interrupt.

4 RFS Enable receive FIFO service request based interrupt.

3 TFS Enable transmit FIFO service request based interrupt.

2:0 — Reserved