7-42 Intel® PXA26x Processor Family Developer’s Manual

Liquid Crystal Display Controller

Note: In dual-panel mode, write to both FBR0 and FBR1 in order to branch properly.

7.6.7 LCD Controller Status Register (LCSR)

The read/write LCD Controller Status Register, described in Table 7-12, contains bits that signal:

• Underrun errors for both the input and output FIFOs

• AC bias pin transition count

• LCD disable and quick disable

• DMA start/end frame and branch status

• DMA transfer bus error conditions.

Unless masked, each of these hardware-detected events signals an interrupt request to the interrupt

controller. Two bits, BER and ABC, generate nonmaskable interrupts.

Each of the LCD’s status bits continues to signal an interrupt request for as long as the bit is set.

Once the bit is cleared, the interrupt is cleared. Status bits are referred to as sticky (once set by

hardware, they must be cleared by software). Writing one to a sticky status bit clears it. Writing

zero has no effect. All LCD interrupts can be masked by programming the Interrupt Controller

Mask Register (ICMR). See Section 4.2, “Interrupt Controller” on page 4-22 for more details.

Write reserved bits with zeros and ignore reads from reserved bits.

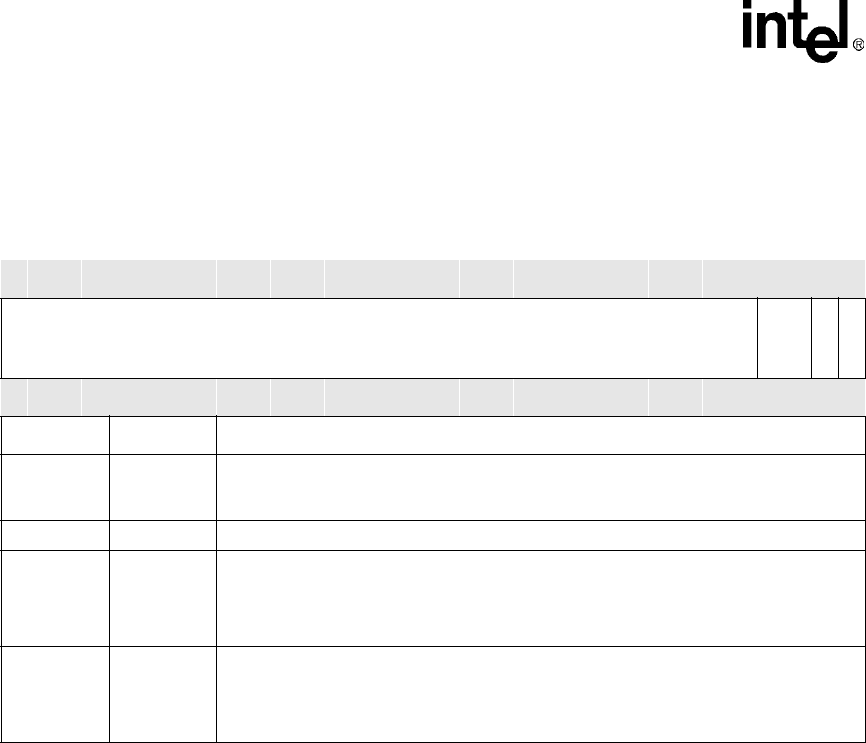

Table 7-11. LCD DMA Frame Branch Registers (FBRx)

Physical Address

channel 0: 0x4400_0020

channel 1: 0x4400_0024

LCD DMA Frame Branch Registers LCD Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Frame Branch Address

Reserved

BINT

BRA

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 X X 0 0

Bits Name Description

31:4

Frame

Branch

Address

FRAME BRANCH ADDRESS:

Address of the descriptor for the branched-to frame.

3:2 — Reserved

1BINT

BRANCH INTERRUPT:

0 – Do not set the BS interrupt bit in register LCSR after the branched-to descriptor is

loaded.

1 – Set the BS interrupt bit in register LCSR after the branched-to descriptor is loaded.

0BRA

BRANCH:

0 – Do not branch after finishing the current frame.

1 – Branch after finishing the current frame. The next descriptor is fetched from the Frame

Branch Address. BRA is automatically cleared after loading the new descriptor.