6-68 Intel® PXA26x Processor Family Developer’s Manual

Memory Controller

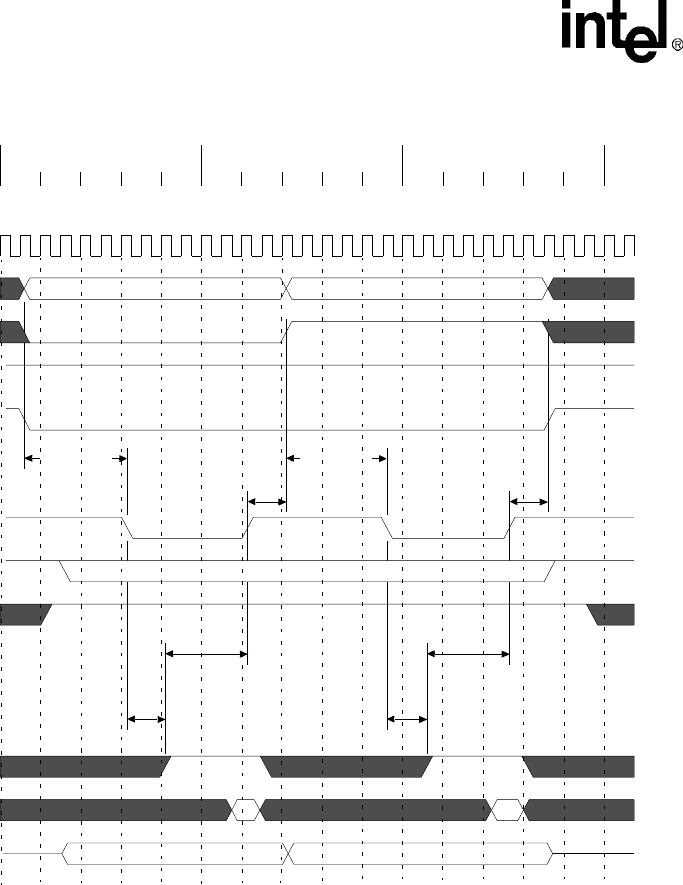

Figure 6-28. 16-Bit PC Card I/O 16-Bit Access to 8-Bit Device

The interface waits the smallest possible amount of time (x_ASST_WAIT) before it checks the

value of the nPWAIT signal. If the nPWAIT signal is asserted (active low), the interface continues

to wait (for a variable number of wait states) until nPWAIT is deasserted. When the nPWAIT signal

is deasserted, the command continues to be asserted for a fixed amount of time (x_ASST_HOLD).

6.10 Companion Chip Interface

The processor can be connected to a companion chip in two different ways:

• Alternate Bus Master Mode

• Variable Latency I/O (See Section 6.8.5, “Variable Latency I/O (VLIO) Interface Overview”)

The connection methods are illustrated in Figure 6-29 and Figure 6-30.

Low Byte High Byte

IOx_ASST_HOLD

IOx_ASST_WAIT + wait states

IOx_ASST_HOLD

IOx_ASST_WAIT + wait states

IOx_HOLD

IOx_SET

IOx_HOLD

IOx_SET

0ns 100ns 200ns 300ns

memclk

MA[25:1],nPREG,PSKTSEL

MA[0]

nPCE2

nPCE1

nPIOW,nPIOR

RDnWR

nIOIS16

nPWAIT

read_data

write_data