Intel® PXA26x Processor Family Developer’s Manual 11-15

Fast Infrared Communication Port

.

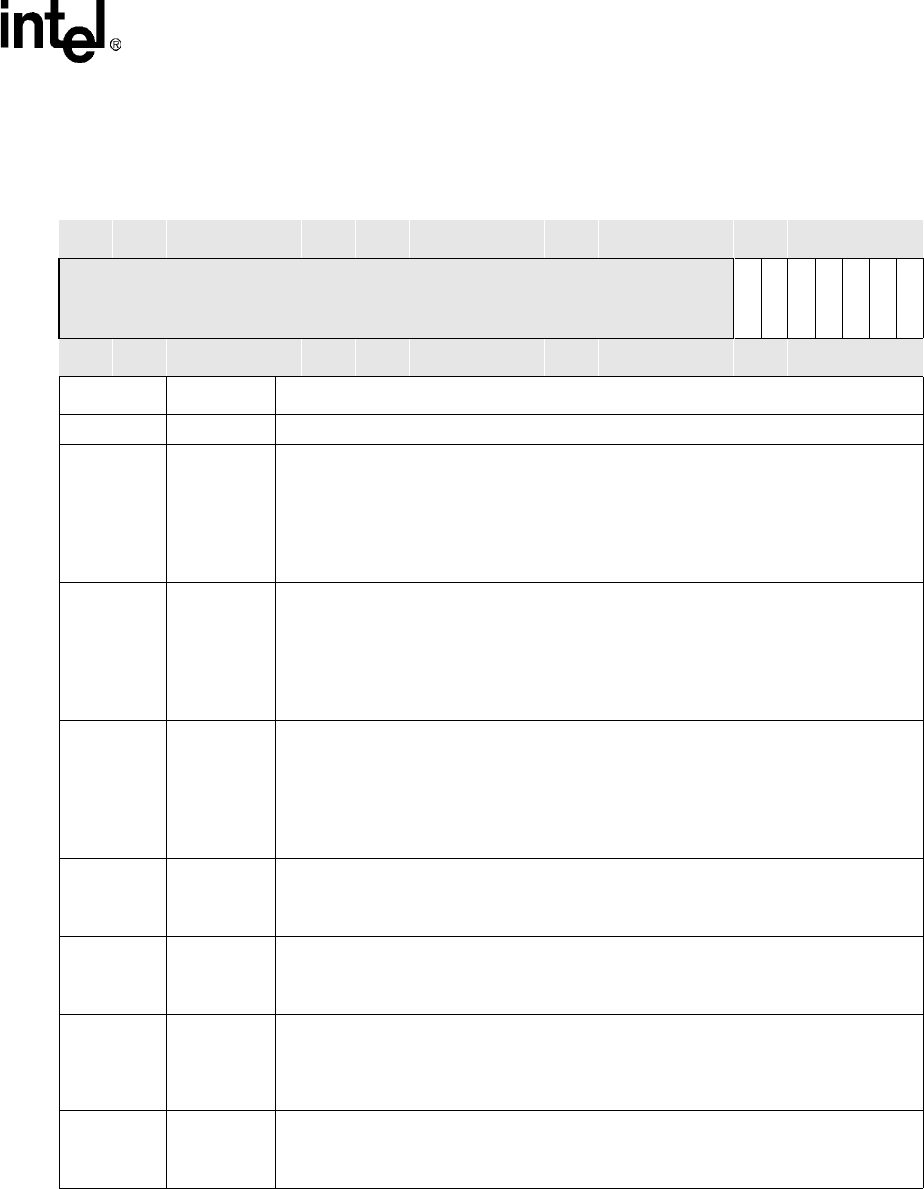

Table 11-7. Fast Infrared Communication Port Status Register 1

0x4080 0018

Fast Infrared Communication Port

Status Register 1 (ICSR1)

FICP

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

ROR

CRE

EOF

TNF

RNE

TBY

RSY

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0

Bits Name Description

[31:7] — Reserved

6ROR

RECEIVE FIFO OVERRUN (read-only):

0 – Receive FIFO has not experienced an overrun.

1 – Receive logic attempted to place data into receive FIFO while it was full. Data

received after the FIFO is full are lost.

Each time an 11-bit value reaches the bottom of the receive FIFO, bit 10 from the last FIFO

entry is transferred to the ROR bit.

5CRE

CRC ERROR (read-only):

0 – CRC not encountered yet or no CRC check errors encountered in the receipt of data.

1 – CRC calculated on the incoming data. Does not match CRC value contained within

the received frame.

Each time an 11-bit value reaches the bottom of the receive FIFO, bit 9 from the last FIFO

entry is transferred to the CRE bit.

4EOF

END OF FRAME (read-only):

0 – Current frame has not completed.

1 – The value at the bottom of the receive FIFO is the last byte of data within the frame,

including aborted frames.

Each time an 11-bit value reaches the bottom of the receive FIFO, bit 8 from the last FIFO

entry is transferred to the EOF bit.

3TNF

TRANSMIT FIFO NOT FULL (read-only):

0 – Transmit FIFO is full.

1 – Transmit FIFO is not full (no interrupt generated).

2RNE

RECEIVE FIFO NOT EMPTY (read-only):

0 – Receive FIFO is empty.

1 – Receive FIFO is not empty (no interrupt generated).

1TBY

TRANSMITTER BUSY FLAG (read-only):

0 – Transmitter is idle (continuous preambles) or disabled.

1 – Transmit logic is currently transmitting a frame (address, control, data, CRC, or start/

stop flag). No interrupt generated.

0RSY

RECEIVER SYNCHRONIZED FLAG (read-only):

0 – Receiver is in hunt mode or is disabled.

1 – Receiver logic is synchronized with the incoming data (no interrupt generated).