Intel® PXA26x Processor Family Developer’s Manual 2-11

System Architecture

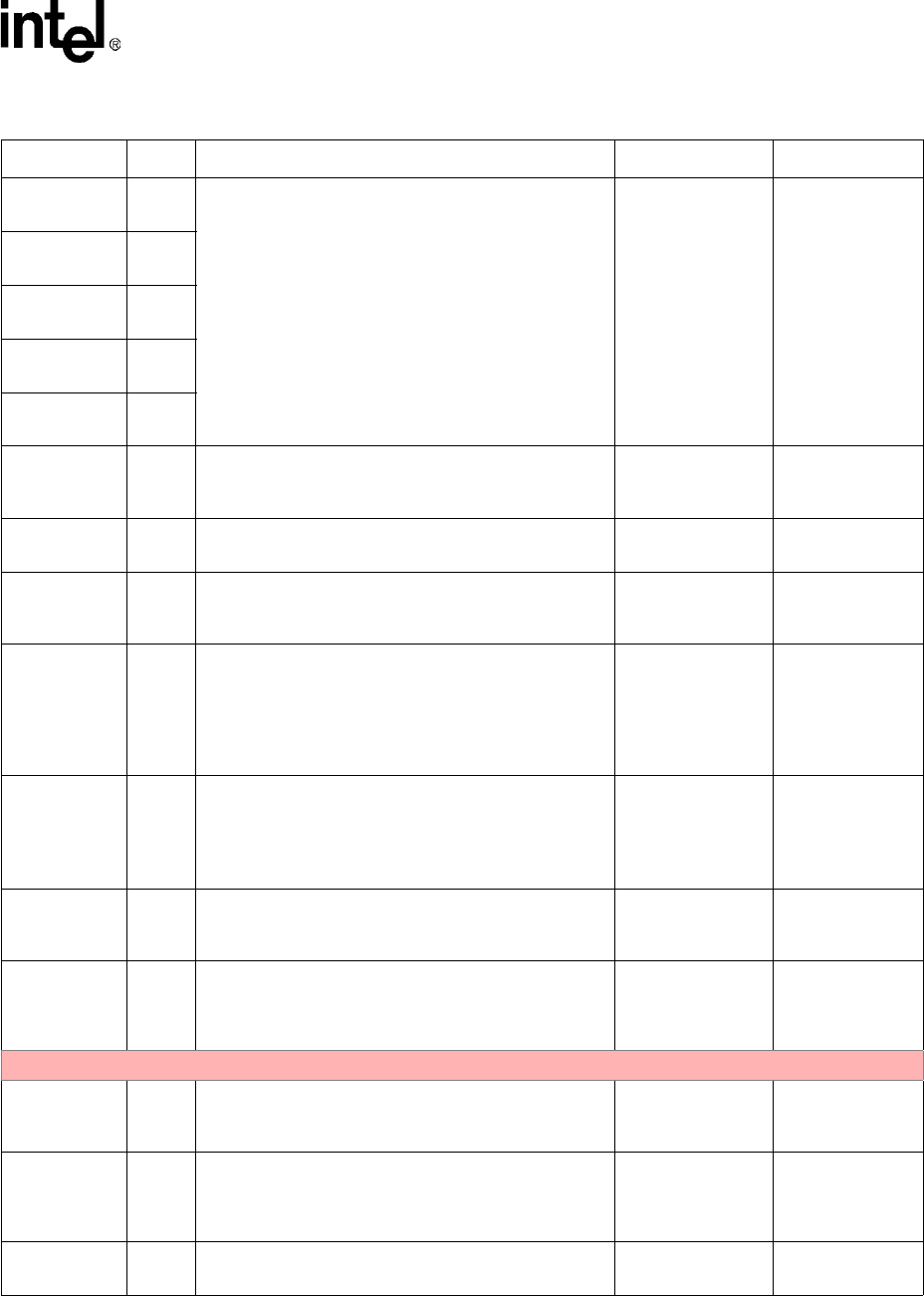

nCS[5]/

GPIO[33]

ICOCZ

STATIC CHIP SELECTS (output):

Chip selects to static memory devices such as ROM and

flash. Individually programmable in the memory

configuration registers. nCS[5:0] can be used with variable

latency I/O devices.

Pulled High

Note [1]

Note [4]

nCS[4]/

GPIO[80]

ICOCZ

nCS[3]/

GPIO[79]

ICOCZ

nCS[2]/

GPIO[78]

ICOCZ

nCS[1]/

GPIO[15]

ICOCZ

nCS[0] ICOCZ

STATIC CHIP SELECT 0 (output):

Chip select for the boot memory. nCS[0] is a dedicated pin

used for internal flash.

Driven High Note [4]

RD/nWR/

GPIO[88]

OCZ

READ/WRITE FOR STATIC INTERFACE (output):

Signals that the current transaction is a read or write.

Driven Low

(but see Note[8])

Driven High (but

see Note[8])

RDY/

GPIO[18]

ICOCZ

VARIABLE LATENCY I/O READY PIN (input):

Notifies the memory controller when an external bus

device is ready to transfer data.

Pulled High

Note [1]

Note [3]

L_DD[8]/

GPIO[66]

ICOCZ

LCD DISPLAY DATA (output):

Transfers pixel information from the LCD Controller to the

external LCD panel.

Memory Controller alternate bus master request. (input)

Allows an external device to request the system bus from

the Memory Controller.

Pulled High

Note [1]

Note [3]

L_DD[15]/

GPIO[73]

ICOCZ

LCD DISPLAY DATA (output):

Transfers pixel information from the LCD Controller to the

external LCD panel.

Memory Controller grant. (output) Notifies an external

device that it has been granted the system bus.

Pulled High

Note [1]

Note [3]

MBGNT/GP[13] ICOCZ

MEMORY CONTROLLER GRANT (output):

Notifies an external device that it has been granted the

system bus.

Pulled High

Note [1]

Note [3]

MBREQ/GP[14] ICOCZ

MEMORY CONTROLLER ALTERNATE BUS MASTER

REQUEST (input):

Allows an external device to request the system bus from

the Memory Controller.

Pulled High

Note [1]

Note [3]

PCMCIA/CF Control Pins

nPOE/

GPIO[48]

ICOCZ

PCMCIA OUTPUT ENABLE (output):

Reads from PCMCIA memory and to PCMCIA attribute

space.

Pulled High

Note [1]

Note [5]

nPWE/

GPIO[49]

ICOCZ

PCMCIA WRITE ENABLE (output):

Performs writes to PCMCIA memory and to PCMCIA

attribute space. Also used as the write enable signal for

Variable Latency I/O.

Pulled High

Note [1]

Note [5]

nPIOW/

GPIO[51]

ICOCZ

PCMCIA I/O WRITE (output):

Performs write transactions to PCMCIA I/O space.

Pulled High

Note [1]

Note [5]

Table 2-6. Pin & Signal Descriptions for the PXA26x Processor Family (Sheet 3 of 12)

Pin Name Type Signal Descriptions Reset State Sleep State