16-34 Intel® PXA26x Processor Family Developer’s Manual

Network/Audio Synchronous Serial Protocol Serial Ports

16.5.7 SSP Data Register (SSDR)

SSDR, shown in Table 16-9, is a single address location that read and write data transfers access.

SSDR represents two physical registers: the first is temporary storage for data on its way out

through the transmit FIFO. The other register is temporary storage for data coming in through the

receive FIFO.

As the system accesses the register, FIFO control logic transfers data automatically between the

registers and FIFOs as fast as the system moves it. Unless attempting a write to a full transmit

FIFO, data in the FIFO shifts up or down to accommodate the new word(s). Status bits show users

whether the FIFO is full, above the programmable trigger threshold, below the programmable

trigger threshold or empty.

For transmit data transfers, the register can be written by the system processor anytime it falls

below its trigger threshold when using programmed I/O.

When a data size of less than 32-bits is selected, do not left-justify data written to the transmit

FIFO. Transmit logic left-justifies the data and ignores any unused bits. Received data of less than

32-bits is automatically right-justified in the receive FIFO.

When the SSP port is programmed for the Microwire* protocol and the size of the Transmit data is

eight bits (SSCR1[MWDS] cleared), the most significant bits are ignored. Similarly, if the size for

the Transmit data is 16 bits (SSCR1[MWDS] set), the most significant 16 bits are ignored.

SSCR0[DSS] controls the Receive data size.

Both FIFOs are cleared when the port is reset, or by clearing SSCR0[SSE].

These are read/write registers. Ignore reads from reserved bits. Write zeros to reserved bits.

16.6 Register Summary

Table 16-10 shows the registers associated with the NSSP port and their physical addresses.

Table 16-11 shows the registers associated with the ASSP port and their physical addresses.

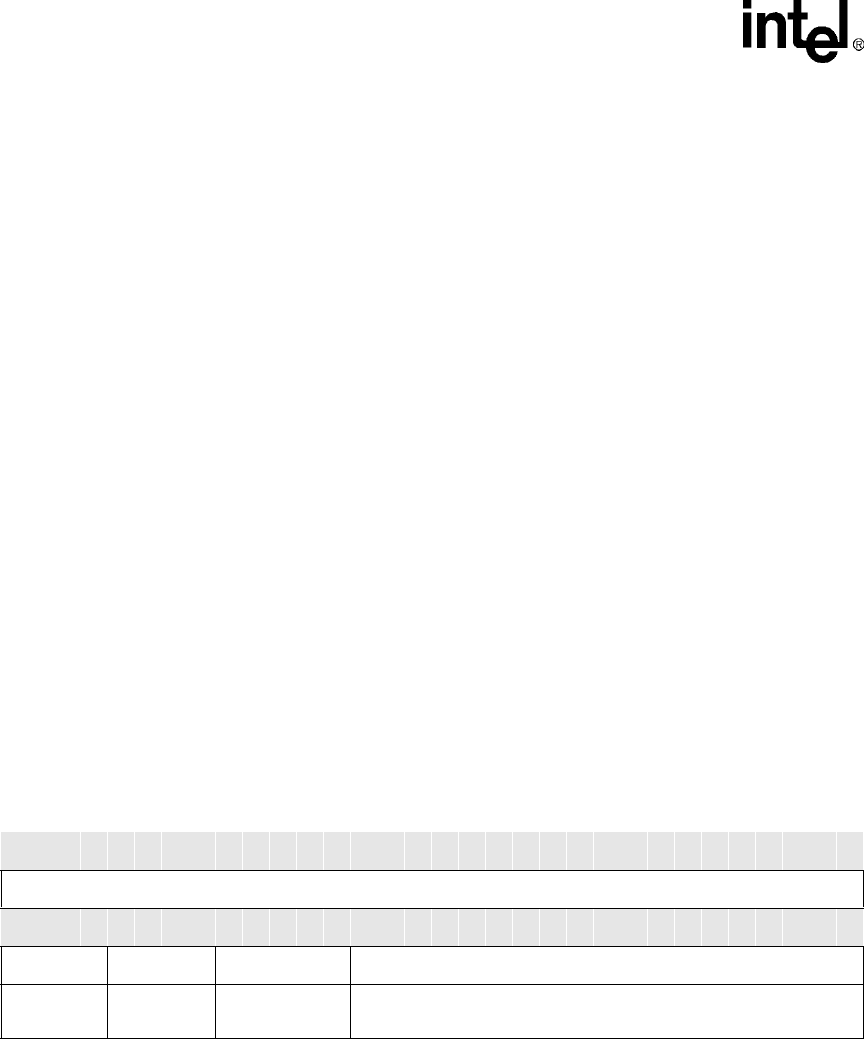

Table 16-9.

SSDR Bit Definitions

Physical Address

Base + 0x10

SSDR

PXA26x processor family Network/Audio

SSP Serial Ports

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

DATA

Reset

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?

Bits Access Name Description

31:0 R/W DATA

TRANSMIT/RECEIVE DATA:

Data word to be written to/read from Transmit/receive FIFO