Intel® PXA26x Processor Family Developer’s Manual 12-37

Universal Serial Bus Device Controller

12.6.7.8 Transmit Short Packet (TSP)

Software uses the transmit short to indicate that the last byte of a data transfer has been sent to the

FIFO. This indicates to the UDC that a short packet or zero-sized packet is ready to transmit.

Software must not set this bit if a packet of 8 bytes is to be transmitted. When the data packet is

successfully transmitted, the UDC clears this bit.

12.6.8 UDC Interrupt Control Register 0 (UICR0)

The UICR0 contains 8 control bits to enable/disable interrupt service requests from data endpoints

0 - 7. All of the UICR0 bits are reset to a 1 so interrupts are not generated on initial system reset.

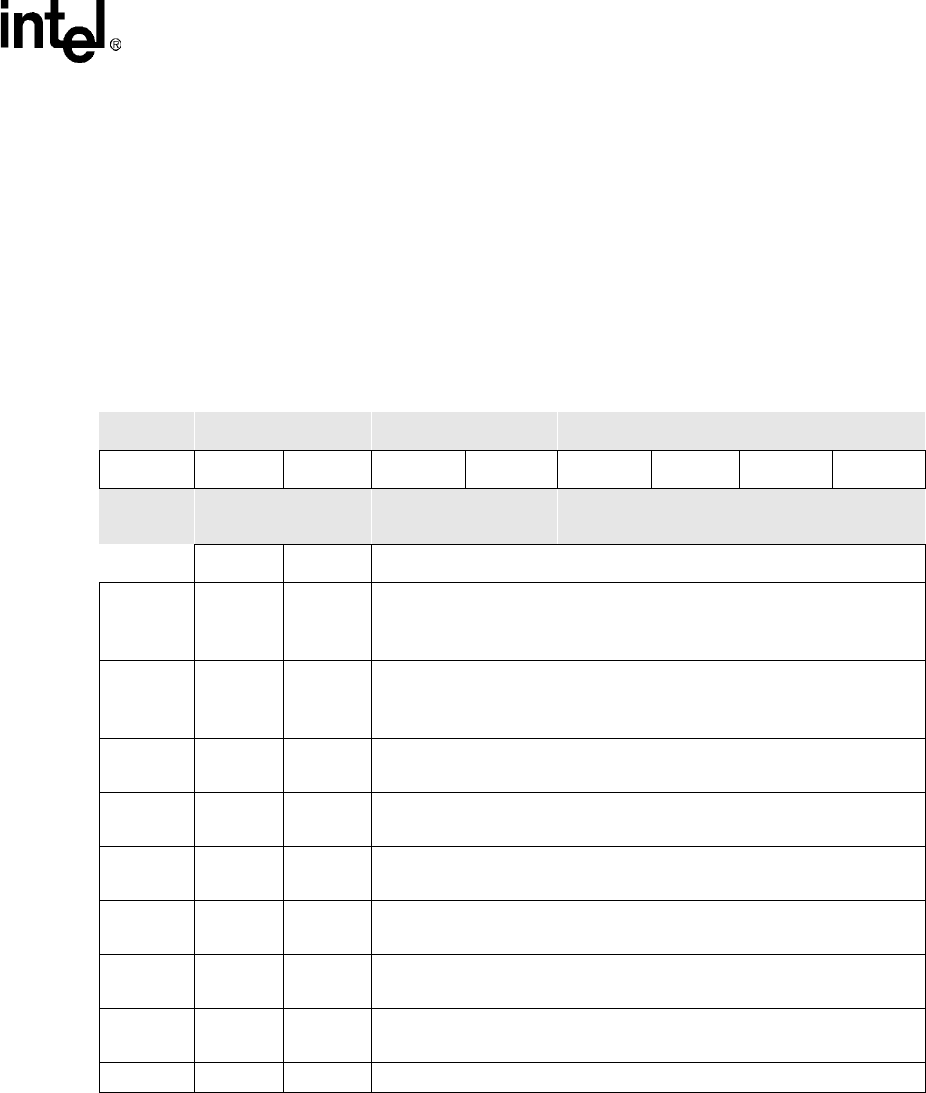

Table 12-18. UDC Endpoint x Control Status Register, Where x is 5, 10, or 15

0h 4060 0024 UDCCS5 Read/Write

0h 4060 0038 UDCCS10 Read/Write

0h 4060 004C UDCCS15 Read/Write

Bit

31:8 7 6 5 4 3 2 1 0

Reserved TSP Reserved FST SST TUR FTF TPC TFS

Rese

t

X 0 0 0 0 0 0 0 1

Bits Name Description

0 TFS

TRANSMIT FIFO SERVICE (read-only):

0 – Transmit FIFO has no room for new data

1 – Transmit FIFO has room for 1 complete data packet

1TPC

TRANSMIT PACKET COMPLETE (read/write 1 to clear):

0 – Error/status bits invalid.

1 – Transmit packet has been sent and error/status bits are valid.

2FTF

FLUSH Tx FIFO (always read 0/ write a 1 to set):

1 – Flush Contents of TX FIFO

3TUR

TRANSMIT FIFO UNDERRUN (read/write 1 to clear):

1 – Transmit FIFO experienced an underrun.

4SST

SENT STALL (read/write 1 to clear):

1 – STALL handshake was sent.

5FST

FORCE STALL (read/write):

1 – Issue STALL handshakes to IN tokens.

6—

Reserved

Always reads 0

7TSP

TRANSMIT SHORT PACKET (read/write 1 to set):

1 – Short packet ready for transmission.

31:8 — Reserved for future Use