Intel® PXA26x Processor Family Developer’s Manual 3-23

Clocks and Power Manager

3.5.1 Power Manager Control Register (PMCR)

Use the PMCR, refer to Table 3-7, to select how sleep mode is entered when the nVDD_FAULT or

the nBATT_FAULT pin is asserted low. When the IDAE bit is set, an imprecise data abort

indication is sent to the CPU. The CPU then performs an abort routine. Software must ensure that

the abort routine sets the sleep mode configuration in the PWRMODE register (see Section 3.7.2,

“Power Mode Register (PWRMODE)”). The IDAE bit is cleared in any reset and when sleep mode

exits. Software may also clear the IDAE bit when necessary. The PMCR must be protected through

Memory Management Unit (MMU) permissions.

This is a read/write register. Ignore reads from reserved bits. Write zeros to reserved bits.

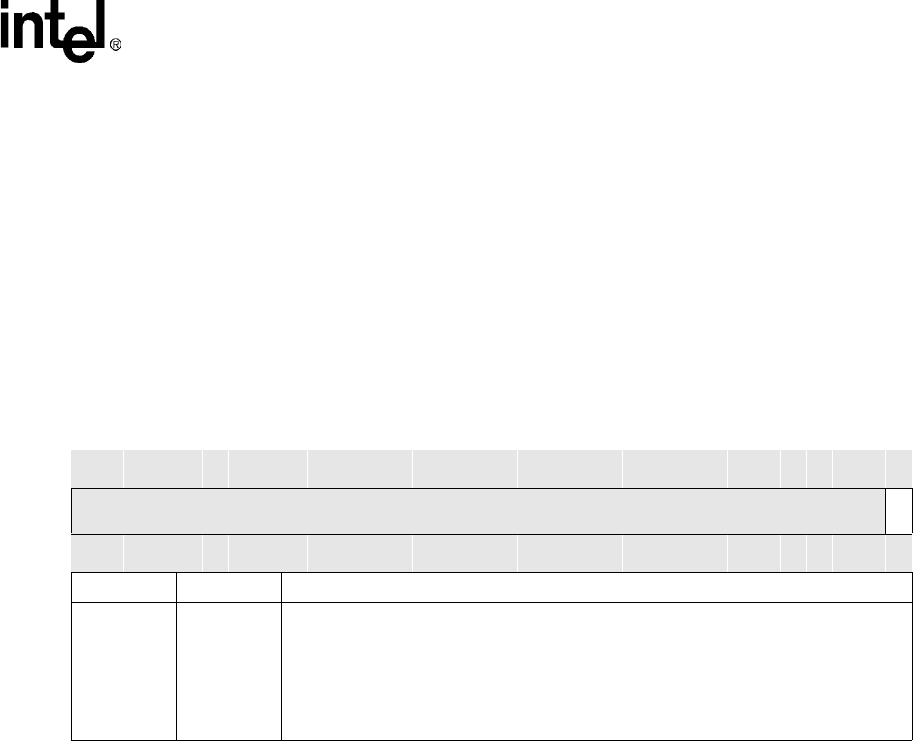

Table 3-7. PMCR Bit Definitions

0x40F0_0000 PMCR Clocks and Power Manager

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

IDAE

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

[31:1] — Reserved

0IDAE

Imprecise Data Abort Enable.

0 – Allow immediate entry to sleep mode when nVDD_FAULT or nBATT_FAULT is

asserted.

1 – Force imprecise data abort signal to CPU to allow software to enter sleep mode

when nVDD_FAULT or nBATT_FAULT is asserted. Recommended mode.

Cleared on hardware, watchdog, and GPIO reset, or when sleep mode exits.