12-30 Intel® PXA26x Processor Family Developer’s Manual

Universal Serial Bus Device Controller

12.6.4.7 Receive FIFO Not Empty (RNE)

The receive FIFO not empty bit indicates that unread data remains in the receive FIFO. This bit

must be polled when the UDCCSx[RPC] bit is set to determine if there is any data in the FIFO that

the DMA did not read. The receive FIFO must continue to be read until this bit clears or data will

be lost.

12.6.4.8 Receive Short Packet (RSP)

The UDC uses the receive short packet bit to indicate that the received OUT packet in the active

buffer currently being read is a short packet or zero-sized packet. This bit is updated by the UDC

after the last byte is read from the active buffer and reflects the status of the new active buffer. If

UDCCSx[RSP] is a one and UDCCSx[RNE] is a 0, it indicates a zero-length packet. If a zero-

length packet is present, the core must not read the data register. UDCCSx[RSP] is cleared when

the next OUT packet is received.

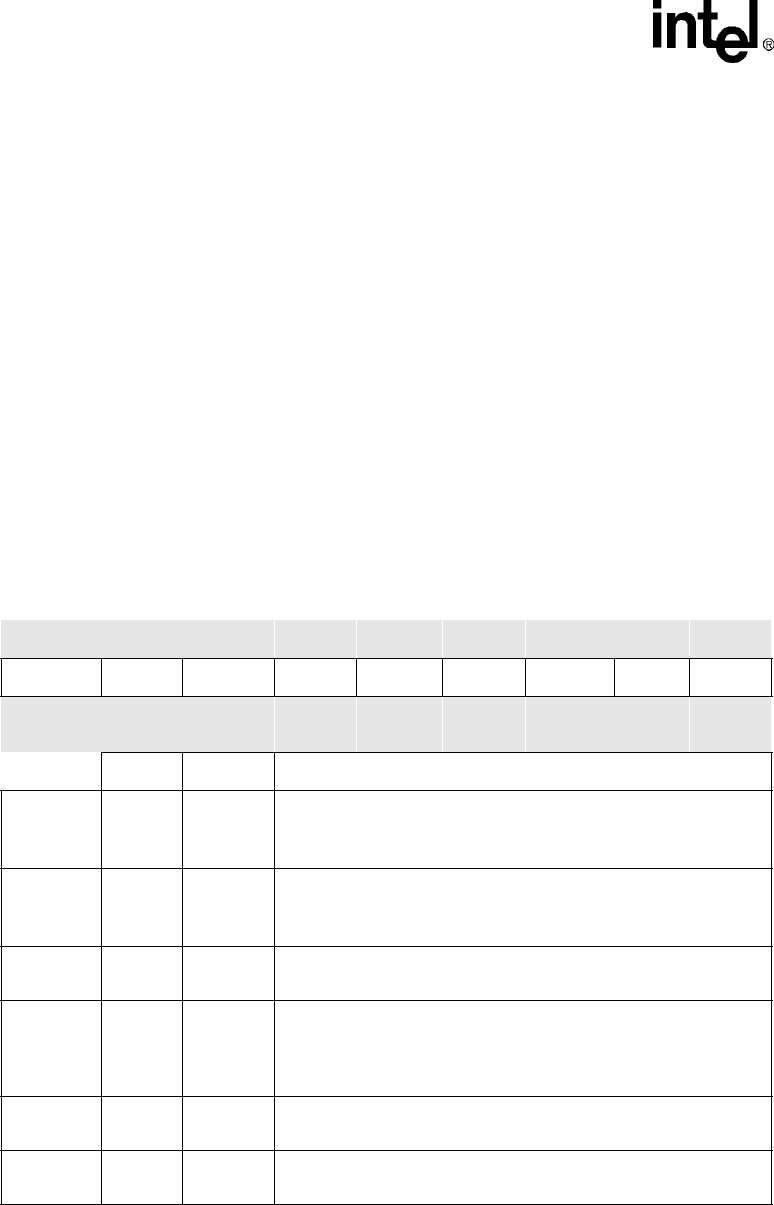

Table 12-15. UDC Endpoint x Control Status Register, Where x is 2, 7, or 12 (Sheet 1 of 2)

0h 4060 0018 UDCCS2 Read/Write

0h 4060 002C UDCCS7 Read/Write

0h 4060 0040 UDCCS12 Read/Write

Bit

31:8 7 6 5 4 3 2 1 0

Reserved RSP RNE FST SST DME Reserved RPC RFS

Rese

t

X 0 0 0 0 0 0 0 0

Bits Name Description

0RFS

RECEIVE FIFO SERVICE (read-only):

0 – Receive FIFO has less than 1 data packet.

1 – Receive FIFO has 1 or more data packets.

1RPC

RECEIVE PACKET COMPLETE (read/write 1 to clear):

0 – Error/status bits invalid.

1 – Receive packet has been received and error/status bits are valid.

2—

Reserved

Always reads zero.

3DME

DMA ENABLE (read/write):

0 – Send data received interrupt after EOP received

1 – Send data received interrupt after EOP received and receive

FIFO has < 32 bytes of data

4 SST

SENT STALL (read/write 1 to clear):

1 – STALL handshake was sent.

5FST

FORCE STALL (read/write):

1 – Issue STALL handshakes to OUT tokens.