7-38 Intel® PXA26x Processor Family Developer’s Manual

Liquid Crystal Display Controller

7.6.5.1 Frame Descriptors

Although the FDADRx registers are loaded by software, the other DMA registers can only be

loaded indirectly from DMA frame descriptors. A frame descriptor is a four-word block, aligned on

a 16-byte boundary, in main memory:

word[0] contains the value for FDADRx

word[1] contains the value for FSADRx

word[2] contains the value for FIDRx

word[3] contains the value for LDCMDx

Software must write the location of the first descriptor to FDADRx before enabling the LCD

controller. Once the controller is enabled, the first descriptor is read, and all four registers are

written by the DMAC. The next frame descriptor pointed to by FDADRx is loaded into the

registers for the associated DMA channel after all data for the current descriptor has been

transferred.

The address in FDADRx is not used when the BRA bit in the Frame Branch Register (FBRx) is set.

In this case, use the frame branch address to fetch the descriptor for the next frame. You can use

branches to load a new palette or to process a regular frame (refer to Section 7.6.6, “LCD DMA

Frame Branch Registers (FBRx)”).

Note: If only one frame buffer is used in external memory, the FDADRx field (word[0] of the frame

descriptor) must point back to itself.

7.6.5.2 LCD DMA Frame Descriptor Address Registers (FDADRx)

Read/write registers FDADR0 and FDADR1, corresponding to DMA channels 0 and 1, contain the

memory address of the next DMA channel descriptor. The DMAC fetches the descriptor at this

location after finishing the current descriptor. On reset, the bits in this register are undefined. The

target address must be aligned to a 16-byte boundary. Bits [3:0] of the address must be zero.

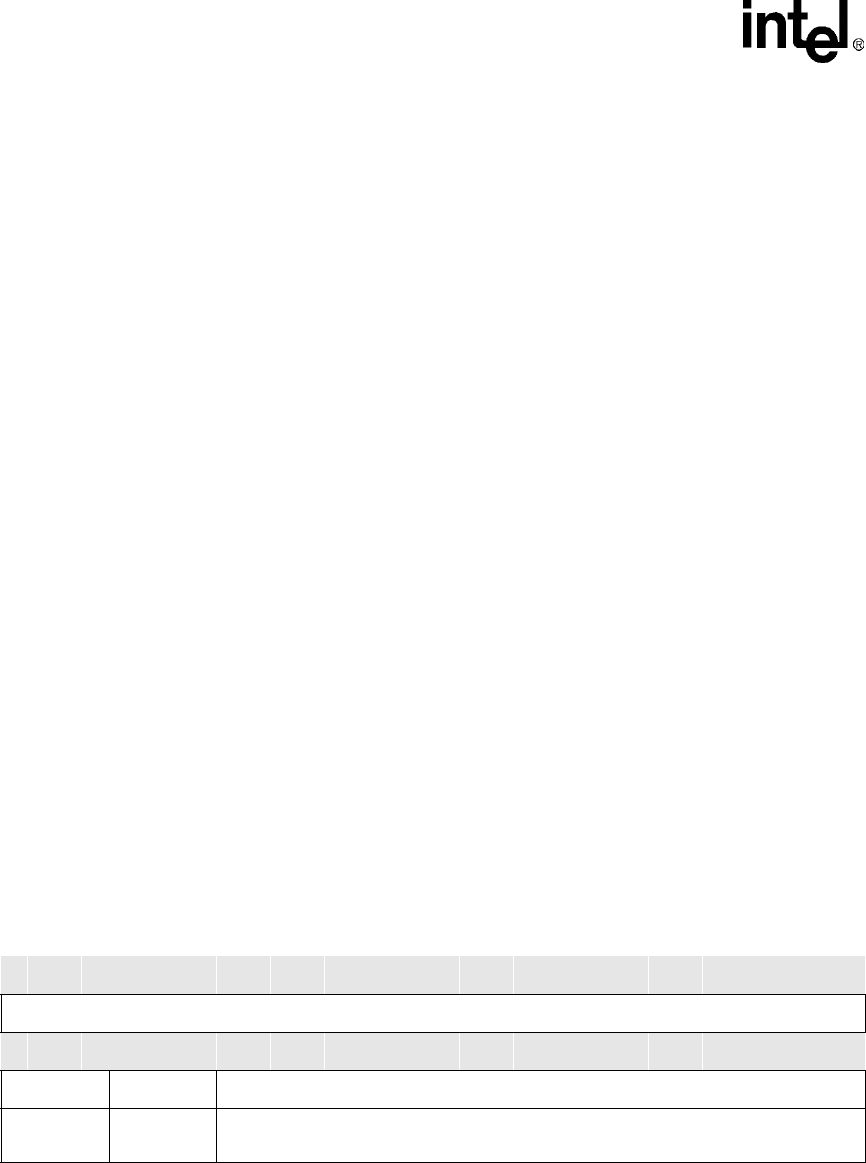

Table 7-7 shows the bit layout.

7.6.5.3 LCD DMA Frame Source Address Registers (FSADRx)

Registers FSADR0 and FSADR1, corresponding to DMA channels 0 and 1, contain the source

address of the current DMA channel descriptor. The address must be aligned on an 8-byte

boundary. Bits [2:0] must be zero. If this descriptor is a palette load, FSADRx points to the

Table 7-7. LCD DMA Frame Descriptor Address Registers

Physical Address

channel 0: 0x4400_0200

channel 1: 0x4400_0210

LCD DMA Frame Descriptor

Address Registers

LCD Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Descriptor Address

Reset

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?

Bits Name Description

31:0

Descriptor

Address

ADDRESS OF NEXT DESCRIPTOR:

Bits [3:0] must be zero for proper memory alignment.