12-38 Intel® PXA26x Processor Family Developer’s Manual

Universal Serial Bus Device Controller

12.6.8.1 Interrupt Mask Endpoint x (IMx), Where x is 0 through 7

The UICR0[IMx] bit is used to mask or enable the corresponding endpoint interrupt request,

USIR0[IRx]. When the mask bit is set, the interrupt is masked and the corresponding bit in the

USIR0 register is not allowed to be set. When the mask bit is cleared and an interruptible condition

occurs in the endpoint, the appropriate interrupt bit is set. Programming the mask bit to a 1 does not

affect the current state of the interrupt bit. It only blocks future zero to one transitions of the

interrupt bit.

12.6.9 UDC Interrupt Control Register 1 (UICR1)

The UICR1 contains 8 control bits to enable/disable interrupt service requests from endpoints 8 –

15. The UICR1 bits are reset to 1 so interrupts are not generated on initial system reset.

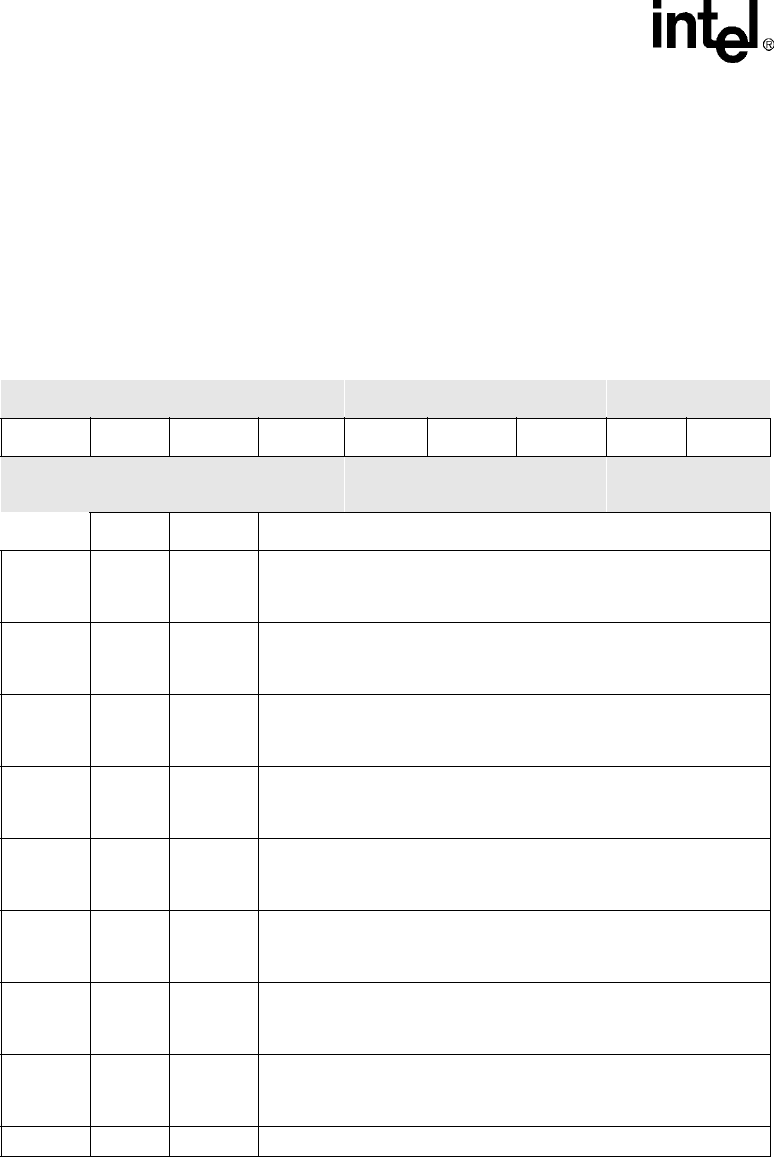

Table 12-19. UDC Interrupt Control Register 0

0h 4060 0050 UICR0 Read/Write

Bit

31:8 7 6 5 4 3 2 1 0

Reserved IM7 IM6 IM5 IM4 IM3 IM2 IM1 IM0

Rese

t

X 1 1 1 1 1 1 1 1

Bits Name Description

0IM0

INTERRUPT MASK FOR ENDPOINT 0:

0 – Endpoint zero interrupt enabled

1 – Endpoint zero interrupt disabled

1IM1

INTERRUPT MASK FOR ENDPOINT 1:

0 – Transmit interrupt enabled

1 – Transmit interrupt disabled

2IM2

INTERRUPT MASK FOR ENDPOINT 2:

0 – Receive interrupt enabled

1 – Receive interrupt disabled

3IM3

INTERRUPT MASK FOR ENDPOINT 3:

0 – Transmit interrupt enabled

1 – Transmit interrupt disabled

4IM4

INTERRUPT MASK FOR ENDPOINT 4:

0 – Receive Interrupt enabled

1 – Receive Interrupt disabled

5IM5

INTERRUPT MASK FOR ENDPOINT 5:

0 – Transmit interrupt enabled

1 – Transmit interrupt disabled

6IM6

INTERRUPT MASK FOR ENDPOINT 6:

0 – Transmit interrupt enabled

1 – Transmit interrupt disabled

7IM7

INTERRUPT MASK FOR ENDPOINT 7:

0 – Receive interrupt enabled

1 – Receive interrupt disabled

31:8 — Reserved for future use