Intel® PXA26x Processor Family Developer’s Manual 14-11

Inter-Integrated Circuit Sound Controller

† SACR1 bits DRPL, DREC, and AMSL cross clock domains. They are registered in an internal clock domain

that is much faster than the BITCLK domain. It takes 4 BITCLK cycles and 4 internal clock cycles before

these controls are conveyed to the slower BITCLK domain. If the above control settings are modified at a rate

faster than (4 BITCLK + 4 internal clock) cycles, the last updated value in this time frame is stored in a

temporary register and is transferred to the BITCLK domain.

14.6.3 Serial Audio Controller I

2

S/MSB-Justified Status Register

(SASR0)

The Serial Audio Status Register (SASR0) is used for recording the status of the FIFOs and

I2SLINK. All bits are read-only. Table 14-7 shows the bit layout of SASR0.

Only 4 bits are assigned for TFL and RFL. Actual fill levels are interpreted as follows:

Actual_TFL(4:0) = {~TNF, TFL(3:0)}

Actual_RFL(4:0) calculation:

if (RFL(3:0) == 4’b0)

Actual_RFL(4:0) = {RNE, RFL(3:0)}

else

Actual_RFL(4:0) = {1’b0, RFL(3:0)}

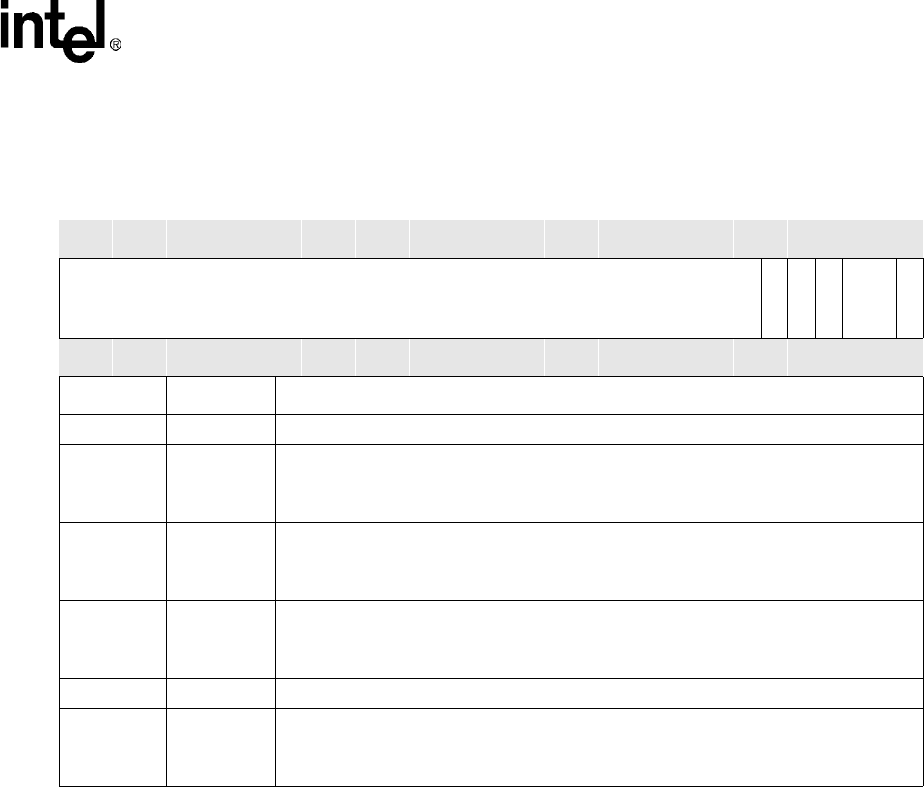

Table 14-6. SACR1 Bit Descriptions

Physical Address

0x4040-0004

Serial Audio Controller I

2

S/MSB-

Justified Control Register

I

2

S Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

ENLBF

DRPL

DREC

Reserved

AMSL

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:6 — Reserved

5ENLBF

ENABLE I

2

S/MSB INTERFACE LOOP BACK FUNCTION:

0 – I

2

S/MSB Interface Loop Back Function is Disabled

1 – I

2

S/MSB Interface Loop Back Function is Enabled

4DRPL

†

DISABLE REPLAYING FUNCTION OF I

2

S OR MSB-JUSTIFIED INTERFACE:

0 – Replaying Function is Enabled

1 – Replaying Function is Disabled

3DREC

†

DISABLE RECORDING FUNCTION OF I

2

S OR MSB-JUSTIFIED INTERFACE:

0 – Recording Function is Enabled

1 – Recording Function is Disabled

2:1 — Reserved

0AMSL

†

SPECIFY ALTERNATE MODE (I

2

S OR MSB-JUSTIFIED) OPERATION:

0 – Select I

2

S Operation Mode

1 – Select MSB-Justified Operation Mode