5-22 Intel® PXA26x Processor Family Developer’s Manual

Direct Memory Access Controller

5.3.6 DMA Target Address Registers

To software, the DMA Target Address Registers (DTADRx) (Figure 5-11) are read only in the

Descriptor Fetch Mode and are read/write in the no-descriptor fetch mode.

These registers contain the target address for the current descriptor in a channel. The target address

is the address of an internal peripheral or a memory location. On power up, the bits in this register

are undefined. If the target address is the address of a companion chip or external peripheral, the

target address must be aligned to an 8-byte boundary. This allows bits [2:0] of the address to be

reserved. If the target address is the address for an internal peripheral, the address must be 32-bit

aligned so that bits [1:0] are reserved. DTADR must not contain the address of any other internal

DMA, LCD, or MEMC register.

The DTADR must not contain a flash address because writes to flash from the DMAC are not

supported.

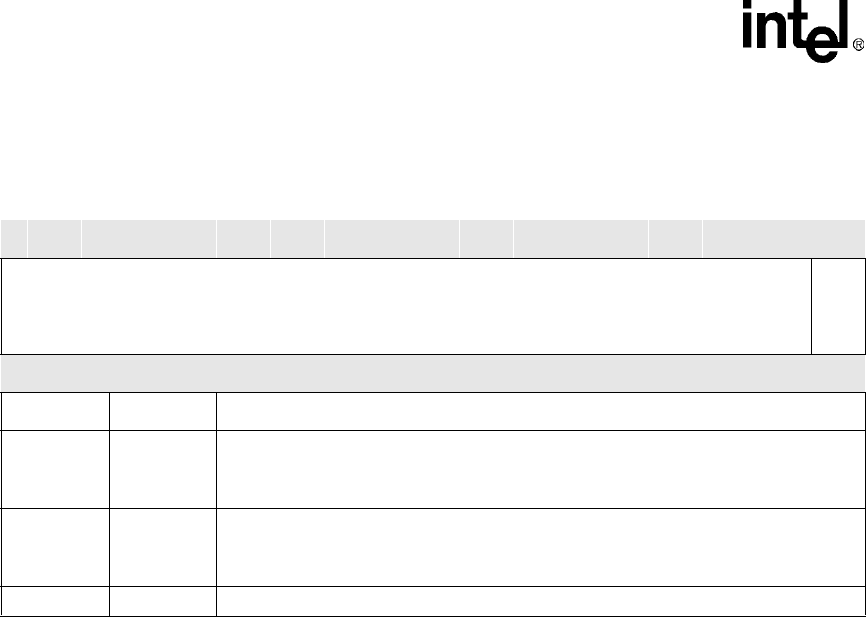

Table 5-10. DSADRx Register Bitmap Bit Definitions

0x4000_02x4

DMA Source Addr Register

(DSADRx)

DMAC

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SOURCE ADDRESS

RESERVED

Reset Uninitialized

Bits Name Description

31:3 SRCADDR

SOURCE ADDRESS (read / write):

Address of the internal peripheral or address of a memory location.

Address of a memory location for companion -chip transfer

2 SRCADDR

SOURCE ADDRESS BIT 2:

RESERVED if DSADR.SrcAddr is an external memory location

Not reserved if DSADR.SrcAddr is an internal peripheral (read / write).

1:0 — Reserved – Read as unknown and must be written as zero.