13-20 Intel® PXA26x Processor Family Developer’s Manual

AC97 Controller Unit

13.8.3.2 Global Control Register

0x4050_0118 MISR Modem In Status Register

0x4050_011C through 0x4050_013C — Reserved

0x4050_0140 MODR Modem FIFO Data Register

0x4050_0144 through 0x4050_01FC — Reserved

(0x4050_0200 through 0x4050_02FC)

with all in increments of 0x00004

— Primary Audio Codec Register

(0x4050_0300 through 0x4050_03FC)

with all in increments of 0x00004

— Secondary Audio Codec Register

(0x4050_0400 through 0x4050_04FC)

with all in increments of 0x0000_0004

— Primary Modem Codec Register

(0x4050_0500 through 0x4050_05FC)

with all in increments of 0x00004

— Secondary Modem Codec Register

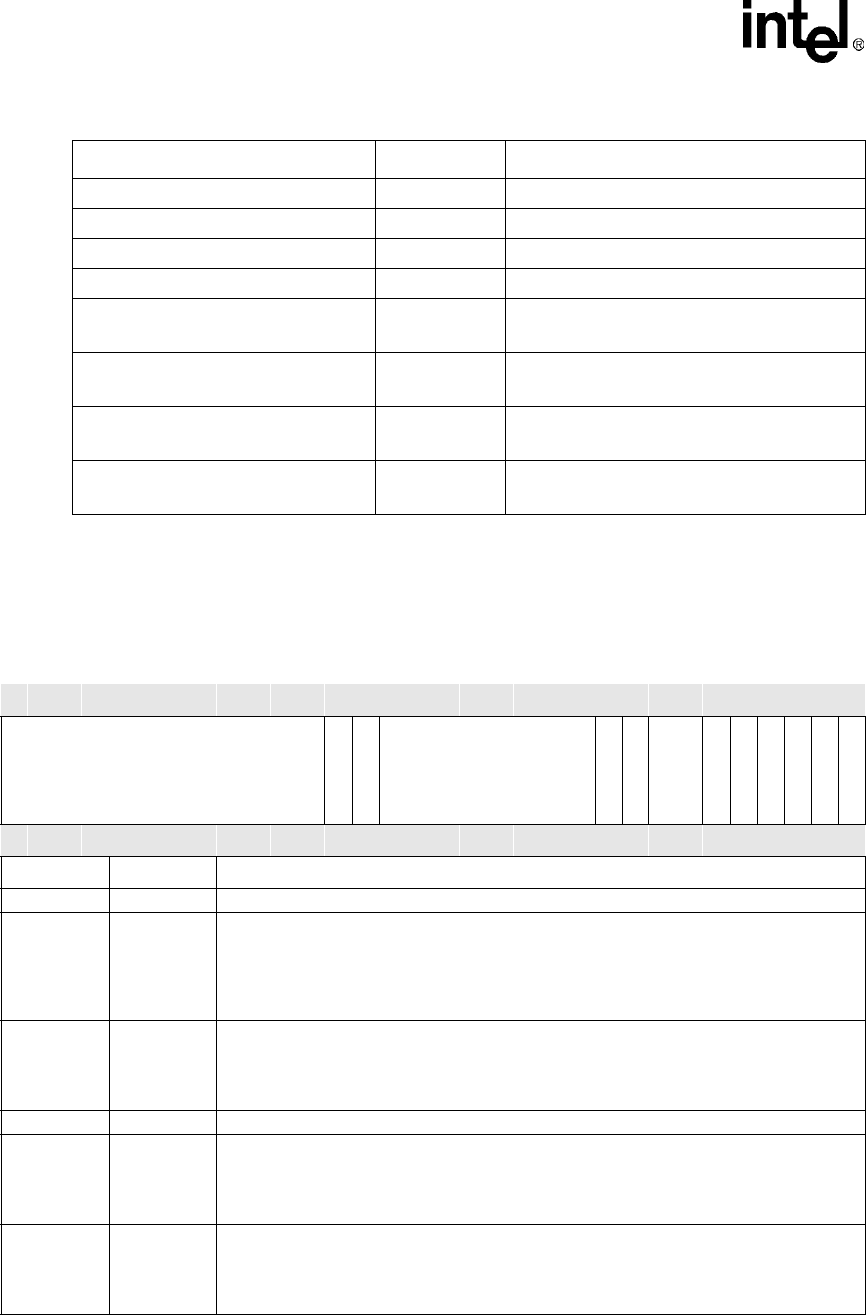

Table 13-8. Global Control Register (Sheet 1 of 2)

Physical Address

4050_000C

GCR Register AC97

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

CDONE_IE

SDONE_IE

Reserved

SECRDY_IEN

PRIRDY_IEN

Reserved

SECRES_IEN

PRIRES_IEN

ACLINK_OFF

WARM_RST

COLD_RST

GIE

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:20 — Reserved

19 CDONE_IE

COMMAND DONE INTERRUPT ENABLE (CDONE_IE):

0 – The controller does not trigger an interrupt to the CPU after sending the command

address and data to the codec.

1 – The controller triggers an interrupt to the CPU after sending the command address and

data to the codec.

18 SDONE_IE

STATUS DONE INTERRUPT ENABLE (SDONE_IE):

0 – Interrupt is disabled

1 – Enables an interrupt to occur after receiving the status address and data from the

codec

17:10 — Reserved

9SECRDY_IEN

SECONDARY READY INTERRUPT ENABLE (SECRDY_IEN):

0 – Interrupt is disabled

1 – Enables an interrupt to occur when the secondary codec sends the codec READY bit

on the SDATA_IN_1 pin

8PRIRDY_IEN

PRIMARY READY INTERRUPT ENABLE (PRIRDY_IEN):

0 – Interrupt is disabled

1 – Enables an interrupt to occur when the primary codec sends the codec READY bit on

the SDATA_IN_0 pin.

Table 13-7. Register Mapping Summary (Sheet 2 of 2)

Address Name Description