Intel® PXA26x Processor Family Developer’s Manual 6-59

Memory Controller

:

13:12 — Reserved

11:7

MCATTx_

ASST

Code for the command assertion time – See Table 6-30 for a description of this code and

its affects on the command assertion.

6:0

MCATTx_

SET

Minimum Number of memory clocks to set up address before command assertion for

MCATT for socket x is equal to MCATTx_SET + 2.

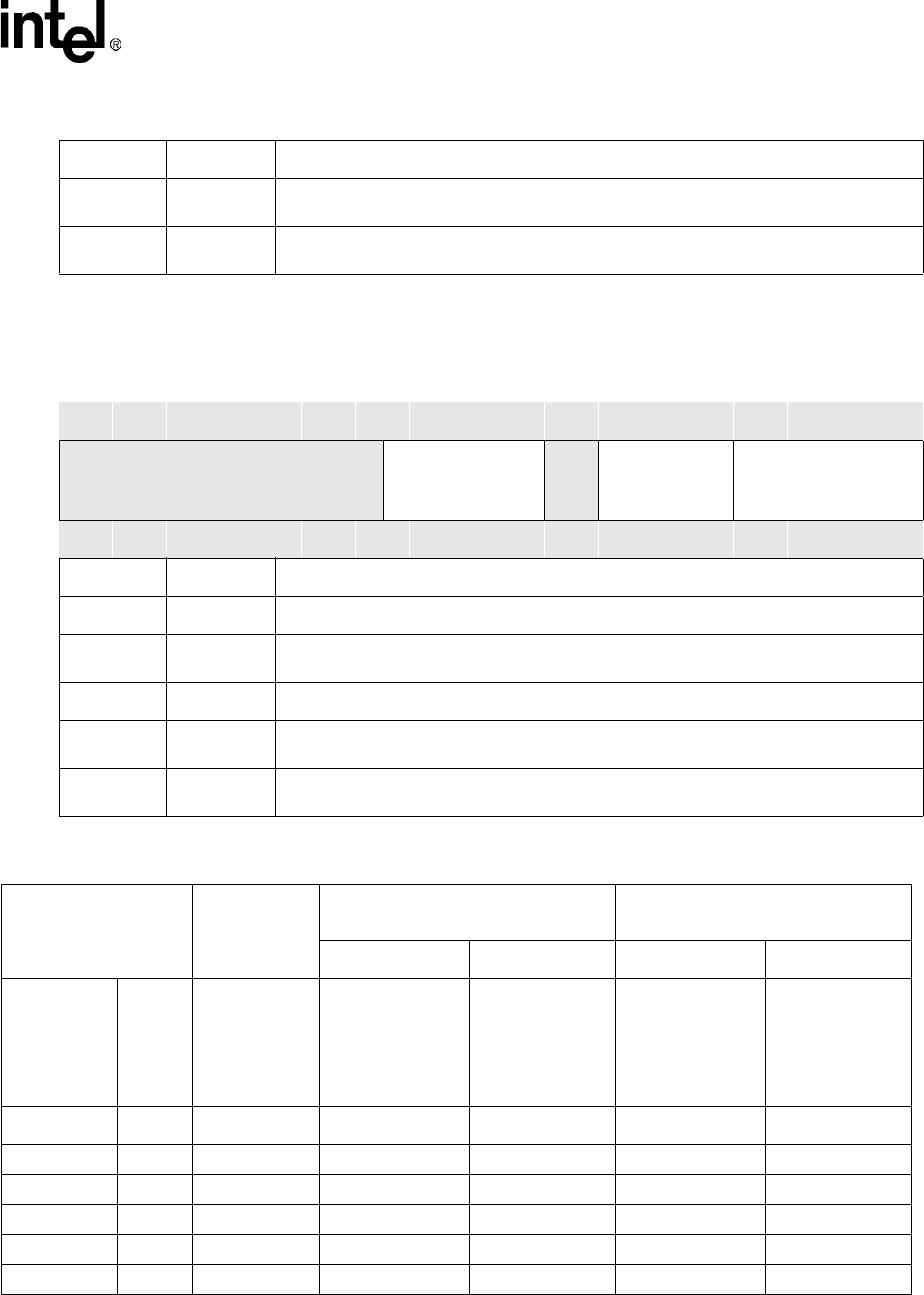

Table 6-29. MCIOx Register Bitmap

0x4800 0038

0x4800 003C

MCIO0

MCIO1

Processor

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved

IOx_

HOLD

Reserved

IOx_

ASST

IOx_

SET

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:20 — Reserved

19:14

MCIOx_

HOLD

Minimum Number of memory clocks to set up address before command assertion for MCIO

for socket x is equal to MCIOx_HOLD + 2.

13:12 — Reserved

11:7

MCIOx_

ASST

Code for the command assertion time. See Table 6-30 for a description of this code and its

affects on the command assertion.

6:0 MCIOx_SET

Minimum Number of memory clocks to set up address before command assertion for MCIO

for socket x is equal to MCIOx_SET + 2.

Table 6-30. Card Interface Command Assertion Code Table

MCMEMx_ASST

MCATTx_ASST

MCIOx_ASST

x_ASST_WAIT

x_ASST_HOLD

x_ASST_WAIT +

x_ASST_HOLD

(nPIOW asserted) (nPIOR asserted) (nPIOW asserted) (nPIOR asserted)

Programmed

Bit Value

Code

decimal

value

# MEMCLKs

(minimum)

to wait before

checking for

nPWAIT=’1’

# MEMCLKs

(minimum)

to assert

command

(nPIOW) after

nPWAIT=’1’

# MEMCLKs

(minimum)

to assert

command

(nPIOR) after

nPWAIT=’1’

# MEMCLKs

(minimum)

command

assertion time

# MEMCLKs

(minimum)

command

assertion time

(Code) (Code) (Code + 2) (2*Code + 3) (2*Code + 4) (3*Code + 5) (3*Code + 6)

00000023456

00001135689

00010 2 4 7 8 11 12

00011 3 5 9 10 14 15

00100 4 6 11 12 17 18

Table 6-28. MCATTx Register Bitmap