8-6 Intel® PXA26x Processor Family Developer’s Manual

Synchronous Serial Port Controller

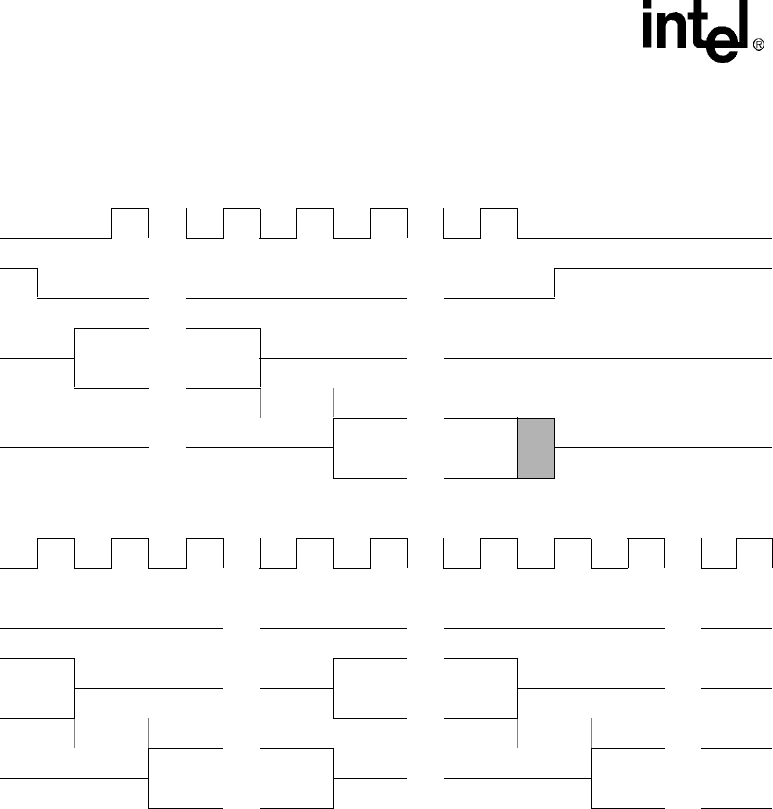

Figure 8-3 shows the National Microwire frame format with 8-bit command words for single and

back-to-back frame transmissions.

8.4.2 Parallel Data Formats for FIFO Storage

Data in the FIFOs is stored with one 16-bit value per data sample with no regard to the format’s

data word length. In each 16-bit field, the stored data sample is right-justified, the word’s least

significant bit is stored in bit 0, and unused bits are packed as zeroes above the most significant bit.

Logic in the SSPC automatically left-justifies data in the transmit FIFO so the sample is properly

transmitted on SSPTXD in the selected frame format.

8.5 FIFO Operation and Data Transfers

Transmit and receive serial data use independent FIFOs. FIFOs are filled or emptied by

programmed I/O or DMA bursts that the DMAC initiates. Bursts may be 4 or 8 half-words in

length during transmission or reception.

Figure 8-3. National Microwire* Frame Format

SSPSCLK

... ...

SSPSFRM

... ...

SSPTXD Bit<7> ... Bit<0> ...

8-Bit Control 1 Clk

SSPRXD ... Bit<N> ... Bit<0>

4 to 16 Bits

Single Transfer

SSPSCLK

... ... ...

SSPSFRM

... ... ...

SSPTXD Bit<0> ... Bit<7> ... Bit<0> ...

1 Clk 1 Clk

SSPRXD Bit<N> ... Bit<0> ... Bit<N> ... Bit<0>

Continuous Transfers