7-40 Intel® PXA26x Processor Family Developer’s Manual

Liquid Crystal Display Controller

7.6.5.5 LCD DMA Command Registers (LDCMDx)

Registers LDCMD0 and LDCMD1, corresponding to DMA channels 0 and 1, contain

configuration fields and the length of the current descriptor for the DMA channel. On reset, the bits

in these register are initialized to zero. Reserved bits must be written with zeros and reads from

reserved bits must be ignored. Table 7-10 shows the bit layout.

These read-only registers are loaded indirectly via the frame descriptors, as described in

Section 7.6.5.1, “Frame Descriptors”.

7.6.5.5.1 Load Palette (PAL)

PAL indicates that data being fetched is loaded into the palette RAM. If PAL=1, the palette RAM is

loaded with the first 8, 32, or 512-bytes of data as:

8 bytes for 1- and 2-bit pixels

32 bytes for 4-bit pixels

512 bytes for 8-bit pixels.

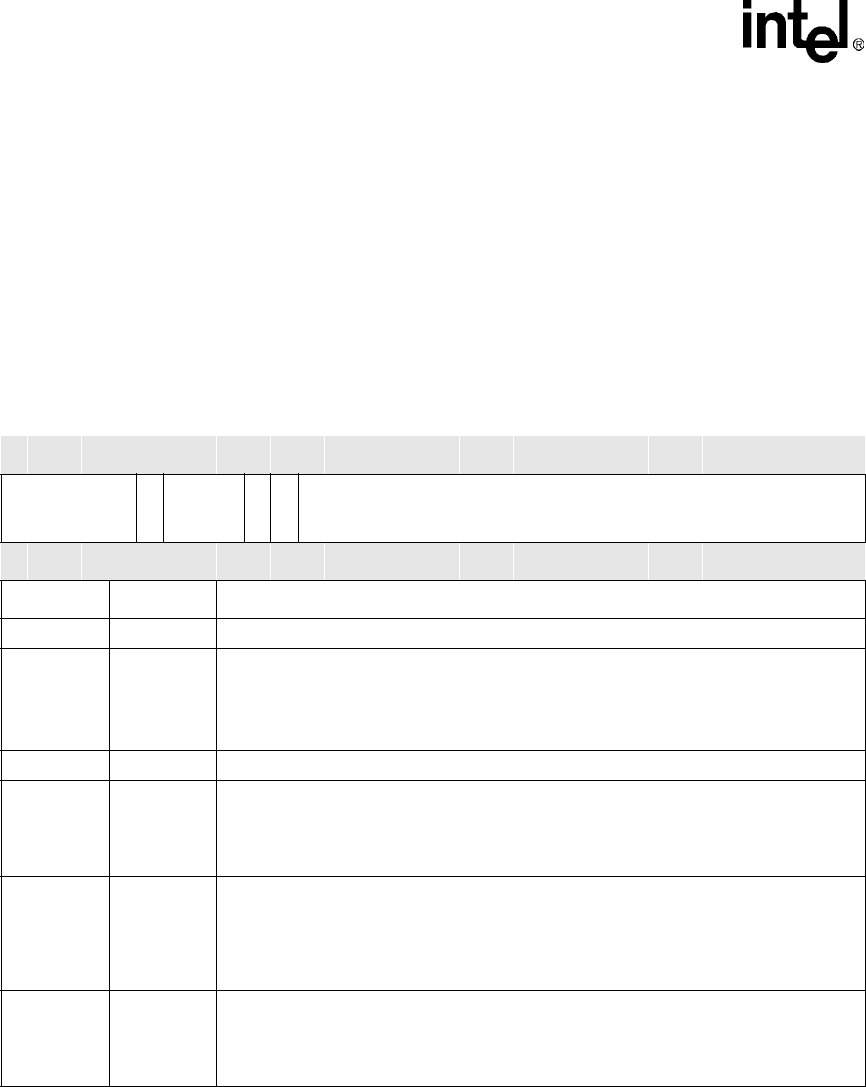

Table 7-10. LCD DMA Command Registers

Physical Address

channel 0: 0x4400_020C

channel 1: 0x4400_021C

LCD DMA Command Registers LCD Controller

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

reserved

PAL

reserved

SOFINT

EOFINT

LEN

Reset

X X X X X 0 X X X 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bits Name Description

31:27 — Reserved

26 PAL

LOAD PALETTE (Section 7.6.5.5.4):

0 – DMA in progress is not the palette buffer.

1 – DMA in progress is the palette buffer.

PAL must not be set in LDCMD1.

25:23 — Reserved

22 SOFINT

START OF FRAME INTERRUPT (Section 7.6.5.5.2):

0 – Do not set the SOF interrupt bit in the LCD status register when starting a new frame.

1 – Set the start of frame (SOF) interrupt bit in the LCD status register when starting a

new frame (after loading the frame descriptor).

21 EOFINT

END OF FRAME INTERRUPT (Section 7.6.5.5.3)

0 – Do not set the EOF interrupt bit in the LCD status register when finished fetching the

last word of this frame.

1 – Set the end of frame (EOF) interrupt bit in the LCD status register when finished

fetching the last word of this frame.

20:0 LEN

LENGTH OF TRANSFER IN BYTES (Section 7.6.5.5.4):

The two lowest bits [1:0] are part of the length calculation but must always be zero for

proper memory alignment.

LEN = 0 is illegal.