Intel® PXA26x Processor Family Developer’s Manual 9-5

Inter-Integrated Circuit Bus Interface Unit

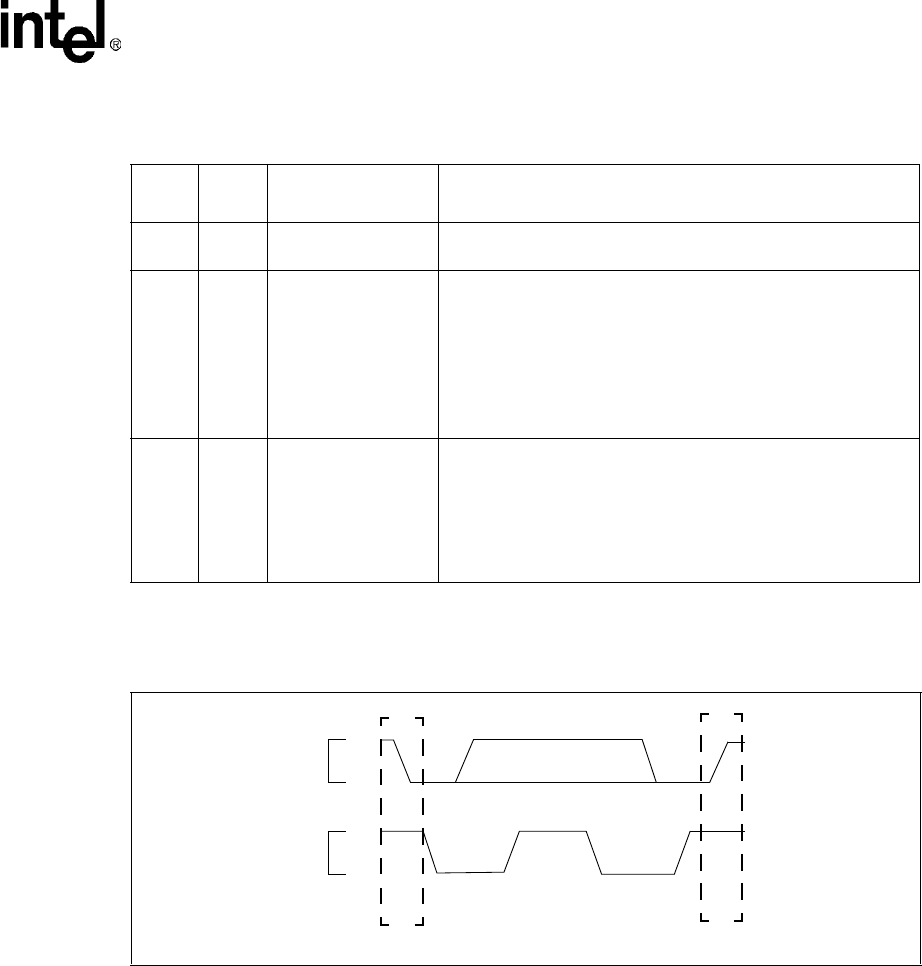

Figure 9-2 shows the relationship between the SDA and SCL lines for START and STOP

conditions.

9.3.3.1 START Condition

The START condition (ICR[START]=1, ICR[STOP]=0) initiates a master transaction or repeated

START. Before it sets the START ICR bit, software must load the

target slave address and the R/

nW bit in the IDBR (see Section 9.9.2, “I2C Data Buffer Register- IDBR”). The START and the

IDBR contents are transmitted on the I

2

C bus after the ICR[TB] bit is set. The I

2

C bus stays in

master-transmit mode for write requests and enters master-receive mode for read requests. For a

repeated start, a change in read or write, or a change in the target slave address, the IDBR contains

the updated target slave address and the R/nW bit. A repeated start enables a master to make

multiple transfers to different slaves without surrendering the bus.

The START condition is not cleared by the I

2

C unit. If the I

2

C loses arbitration while initiating a

START, it may re-attempt the START when the bus is freed. See Section 9.4.4, “Arbitration” for

details on how the I

2

C unit functions in those circumstances.

Table 9-4. START and STOP Bit Definitions

STOP

bit

STAR

T bit

Condition Notes

0 0 No START or STOP

I

2

C unit sends a no START or STOP condition. Used when

multiple data bytes need to be transferred.

01

START Condition and

Repeated START

I

2

C unit sends a START condition and transmit the 8-bit IDBR’s

contents. The IDBR must contain the 7-bit address and the R/nW

bit before a START is initiated.

For a repeated start, the IDBR contains the target slave address

and the R/nW bit. This allows a master to make multiple transfers

to different slaves without giving up the bus.

The interface stays in master-transmit mode for writes and

transitions to master-receive mode for reads.

1 X STOP Condition

In master-transmit mode, the I

2

C unit transmits the 8-bit IDBR and

sends a STOP condition on the I

2

C bus.

In master-receive mode, the ICR[ACKNAK] must be changed to a

negative ACK (see Section 9.4.3, “Inter-Integrated Circuit

Acknowledge”). The I

2

C unit transmits the NAK bit, receives the

data byte in the IDBR, and sends a STOP condition on the I

2

C

bus.

Figure 9-2. Start and Stop Conditions

SDA

SCL

Start Condition

~

~

~

~

~

~

Stop Condition