Intel® PXA26x Processor Family Developer’s Manual 15-35

MultiMediaCard Controller

15.5.16 MMC_RES FIFO (read only)

The MMC_RES FIFO contains the response after a command. It is 16 bits wide by eight

entries.The RES FIFO does not contain the 7-bit CRC for the response. The status for CRC

checking and response time-out status is in the status register, MMC_STAT (see Table 15-22).

The first half-word read from the response FIFO is the most significant half-word of the received

response.

15.5.17 MMC_RXFIFO FIFO (read only)

The MMC_RXFIFO consists of two dual FIFOs, where each FIFO is eight bits wide by 32 entries

deep. This FIFO holds the data read from a card. It is a read only FIFO to the software, and is read

on 8-bit boundaries. The eight bits of data are read on a 32-bit boundary and occupying the least

significant byte lane (7:0) (see Table 15-23).

15.5.18 MMC_TXFIFO FIFO

The MMC_TXFIFO consists of two dual FIFOs, where each FIFO is eight bits wide by 32 entries

deep. This FIFO holds the data to be written to a card. It is a write only FIFO to the software, and is

written on boundaries eight bits wide. The eight bits of data are written on a 32-bit APB and

occupy the least significant byte lane (7:0) (see Table 15-24 on page 15-36).

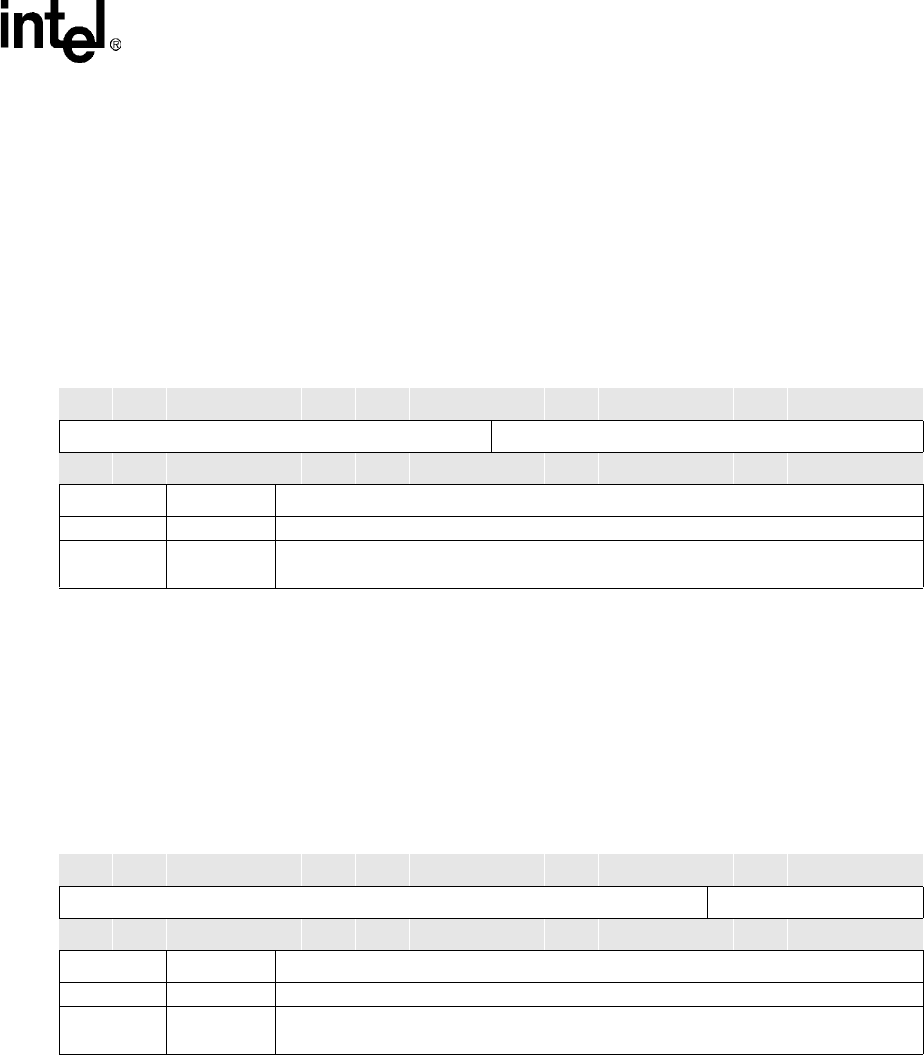

Table 15-22. MMC_RES, FIFO Entry

Physical Address

4110_003c

MMC_RES FIFO Entry MMC

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved RESPONSE_DATA

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 x x x x x x x x x x x x x x x x

Bits Name Description

31:16 — Reserved

15:0

RESPONSE_

DATA

RESPONSE DATA:

Two bytes of response data

Table 15-23. MMC_RXFIFO, FIFO Entry

Physical Address

4110_0040

MMC_RXFIFO Entry MMC

Bit

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Reserved READ_DATA

Reset

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 x x x x x x x x

Bits Name Description

31:8 — Reserved

7:0 READ_DATA

READ DATA:

One byte of read data