Intel® PXA26x Processor Family Developer’s Manual 12-31

Universal Serial Bus Device Controller

12.6.5 UDC Endpoint x Control/Status Register (UDCCSx), Where

x is 3, 8, or 13

The UDC endpoint(x) control status register contains 4 bits that operate endpoint(x), an

isochronous IN endpoint.

12.6.5.1 Transmit FIFO Service (TFS)

The transmit FIFO service bit is be set if one or fewer data packets remain in the transmit FIFO.

UDCCSx[TFS] is cleared when two complete data packets are in the FIFO. A complete packet of

data is signified by loading 256 bytes or by setting UDCCSx[TSP].

12.6.5.2 Transmit Packet Complete (TPC)

The the UDC sets transmit packet complete bit when an entire packet is sent to the host. When this

bit is set, the IRx bit in the appropriate UDC status/interrupt register is set if transmit interrupts are

enabled. This bit can be used to validate the other status/error bits in the endpoint(x) control/status

register. The UDCCSx[TPC] bit gets cleared by writing a one to it. This clears the interrupt source

for the IRx bit in the appropriate UDC status/interrupt register, but the IRx bit must also be cleared.

Setting this bit does not prevent the UDC from transmitting the next buffer. The UDC issues NAK

handshakes to all IN tokens if this bit is set and neither buffer has been triggered by writing

64 bytes or setting UDCCSx[TSP].

When DMA is used to load the transmit buffers, the interrupt generated by UDCCSx[TPC] can be

masked to allow data to be transmitted without core intervention.

6RNE

RECEIVE FIFO NOT EMPTY (read-only):

0 – Receive FIFO empty.

1 – Receive FIFO not empty.

7RSP

RECEIVE SHORT PACKET (read-only):

1 – Short packet received and ready for reading.

31:8 Reserved Reserved for future use

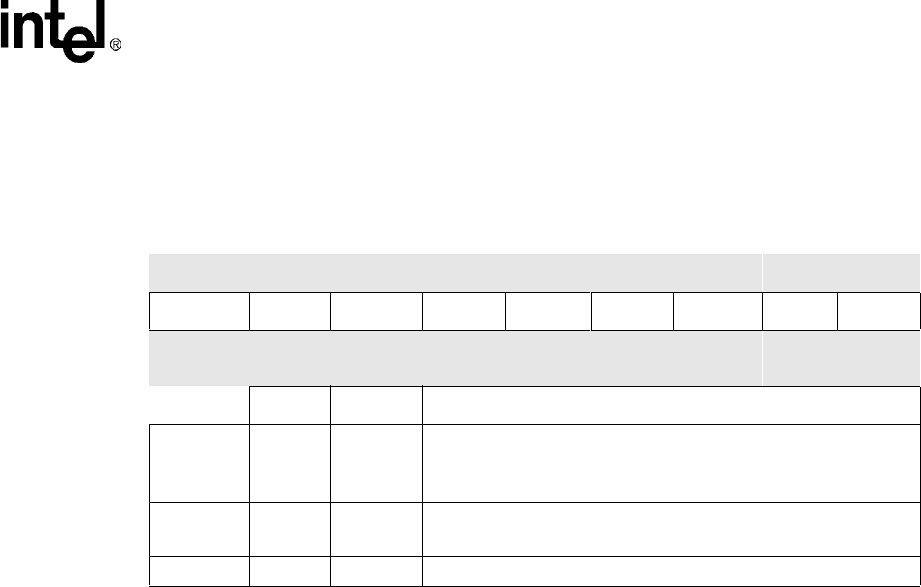

Table 12-15. UDC Endpoint x Control Status Register, Where x is 2, 7, or 12 (Sheet 2 of 2)

0h 4060 0018 UDCCS2 Read/Write

0h 4060 002C UDCCS7 Read/Write

0h 4060 0040 UDCCS12 Read/Write

Bit

31:8 7 6 5 4 3 2 1 0

Reserved RSP RNE FST SST DME Reserved RPC RFS

Rese

t

X 0 0 0 0 0 0 0 0

Bits Name Description