Interrupts

5-21

Program Control

1 to the corresponding IFR bit. All pending interrupts can be cleared by writing

the current contents of the IFR back into the IFR. Acknowledgement of a

hardware request also clears the corresponding IFR bit. A device reset clears

all IFR bits.

Notes:

1) When an interrupt is requested by an INTR instruction, if the correspond-

ing IFR bit is set, the CPU will not clear it automatically. If an application

requires that the IFR bit be cleared, the bit must be cleared in the inter-

rupt service routine.

2) To avoid double interrupts from the synchronous serial port and the

asynchronous serial port (including delta interrupts), clear the IFR bit(s)

in the corresponding interrupt service routine, just before returning from

the routine.

For ’C2xx devices other than the ’C209, Figure 5–7 shows the IFR. Descrip-

tions of the bits follow the figure. For a description of the ’C209 IFR, see sub-

section 11.3.1,

’C209 Interrupt Registers

, on page 11-11.

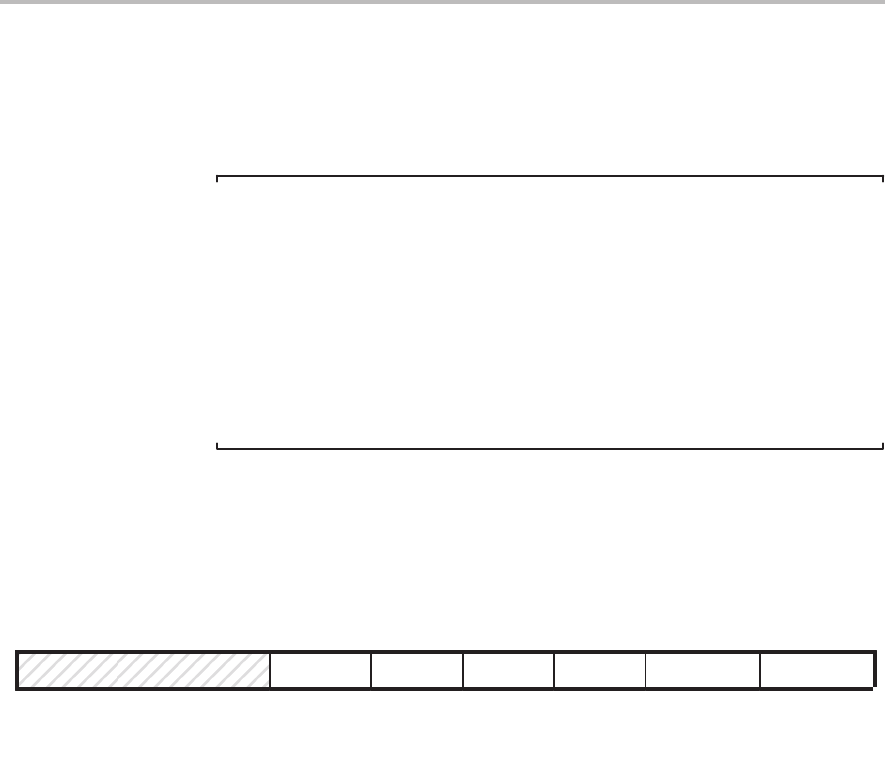

Figure 5–7. ’C2xx Interrupt Flag Register (IFR) — Data-Memory Address 0006h

15 6 5 4 3 2 1 0

Reserved TXRXINT XINT RINT TINT INT2/INT3 HOLD/INT1

0 R/W1C–0 R/W1C–0 R/W1C–0 R/W1C–0 R/W1C–0 R/W1C–0

Note: 0 = Always read as zeros; R = Read access; W1C = Write 1 to this bit to clear it to 0;

value following dash (–) is value after reset.

Bits 15–6 Reserved. Bits 15–6 are reserved and are always read as 0s.

Bit 5 TXRXINT — Transmit/receive interrupt flag. Bit 5 is tied to the transmit/receive in-

terrupt for the asynchronous serial port.

To avoid double interrupts, write a 1 to this

bit in the interrupt service routine.

TXRXINT = 0 Interrupt TXRXINT is not pending.

TXRXINT = 1 Interrupt TXRXINT is pending.

Bit 4 XINT — Transmit interrupt flag. Bit 4 is tied to the transmit interrupt for the synchro-

nous serial port.

To avoid double interrupts, write a 1 to this bit in the interrupt service

routine.

XINT = 0 Interrupt XINT is not pending.

XINT = 1 Interrupt XINT is pending.