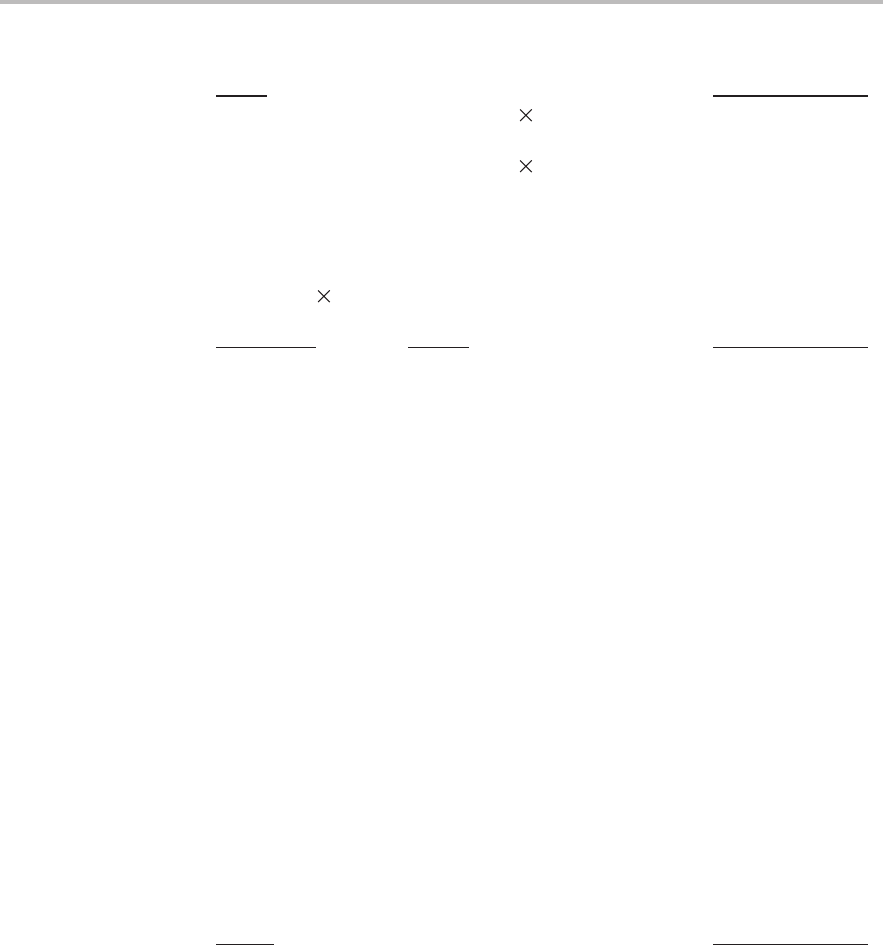

ADD

Add to Accumulator

7-24

Execution Increment PC, then ...

Event Addressing mode

(ACC) + ((data-memory address) 2

shift

) → ACC Direct or indirect

(ACC) + ((data-memory address) 2

16

) → ACC Direct or indirect

(shift of 16)

(ACC) + k → ACC Short immediate

(ACC) + lk 2

shift

→ ACC Long immediate

Status Bits

Affected by Affects Addressing mode

SXM and OVM C and OV Direct or indirect

OVM C and OV Short immediate

SXM and OVM C and OV Long immediate

Description The content of the addressed data memory location or an immediate constant

is left-shifted and added to the accumulator. During shifting, low-order bits are

zero filled. High-order bits are sign extended if SXM = 1 and zero filled if

SXM = 0. The result is stored in the accumulator. When short immediate ad-

dressing is used, the addition is unaffected by SXM and is not repeatable.

If you are using indirect addressing and update the ARP, you must specify a

shift operand. However, if you do not want a shift to occur, enter a 0 for this

operand. For example:

ADD *+,0,AR2

Normally, the carry bit is set (C = 1) if the result of the addition generates a carry

and is cleared (C = 0) if it does not generate a carry. However, when adding

with a shift of 16, the carry bit is set if a carry is generated but otherwise, the

carry bit is unaffected. This allows the accumulator to generate the proper

single carry when adding a 32-bit number to the accumulator.

Words

Words Addressing mode

1 Direct, indirect, or

short immediate

2 Long immediate