NMI

Nonmaskable Interrupt

7-124

Syntax NMI

Operands None

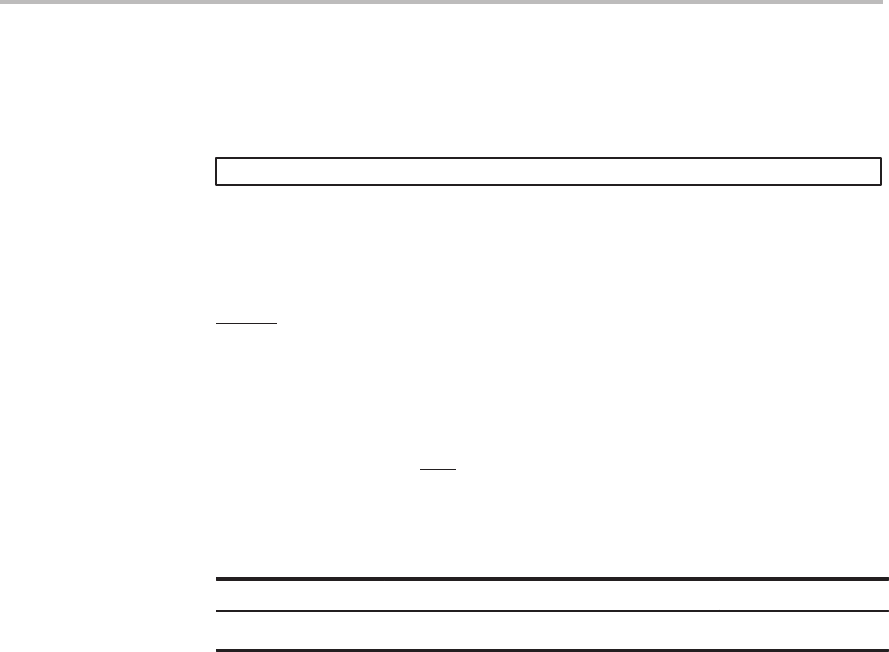

Opcode

0123456789101112131415

0100101001111101

Execution (PC) + 1 → stack

24h → PC

1 → INTM

Status Bits

Affects

INTM

This instruction is not affected by INTM.

Description The NMI instruction forces the program counter to the nonmaskable interrupt

vector located at 24h. This instruction has the same effect as the hardware

nonmaskable interrupt NMI

.

Words 1

Cycles for a Single NMI Instruction

ROM DARAM SARAM External

4 4 4 4+3p

†

†

The ’C2xx performs speculative fetching by reading two additional instruction words. If the PC

discontinuity is taken, these two instruction words are discarded.

Example NMI ;PC + 1 is pushed onto the stack, and then

;control is passed to program memory location

;24h.

Cycles